## **Features**

- AVR High Performance and Low Power RISC Architecture

- 120 Powerful Instructions Most Single Clock Cycle Execution

- 8K bytes of In-System Reprogrammable Flash

- SPI Serial Interface for Program Downloading

- Endurance: 1,000 Write/Erase Cycles

- 512 bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 512 bytes Internal SRAM

- 32 x 8 General Purpose Working Registers

- 32 Programmable I/O Lines

- Programmable Serial UART

- SPI Serial Interface

- V<sub>CC</sub>: 2.7 6.0V

- Fully Static Operation, 0 8 MHz (4.0 6.0V), 0 4 MHz (2.7 4.0V)

- Up to 8 MIPS Throughput at 8 MHz

- One 8-Bit Timer/Counter with Separate Prescaler

- One 16-Bit Timer/Counter with Separate Prescaler and Compare and Capture Modes

- Dual PWM

- External and Internal Interrupt Sources

- Programmable Watchdog Timer with On-Chip Oscillator

- On-Chip Analog Comparator

- Low Power Idle and Power Down Modes

- Programming Lock for Software Security

# **Description**

The AT90S8515 is a low-power CMOS 8-bit microcontroller based on the AVR <sup>®</sup> enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S8515 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

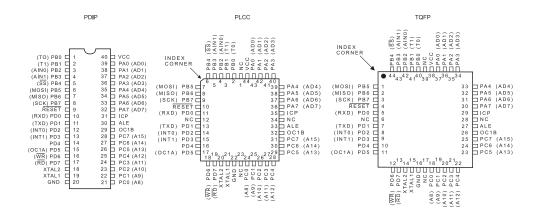

# **Pin Configurations**

8-Bit AVR®

Microcontroller

with 8K bytes

In-System

Programmable

Flash

AT90S8515 Preliminary

Rev. 0841C-02/98

# **Block Diagram**

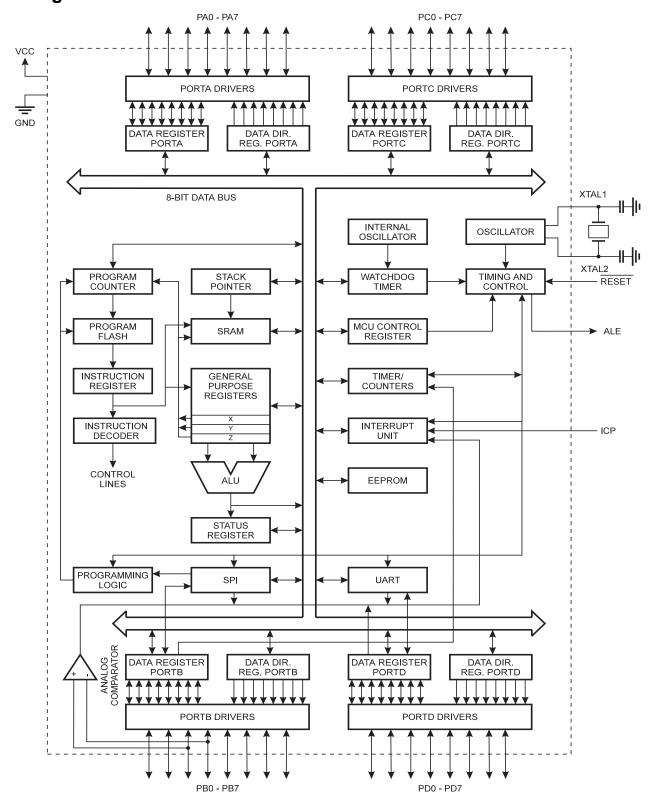

Figure 1. The AT90S8515 Block Diagram

# **Description** (Continued)

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The AT90S8515 provides the following features: 8K bytes of Downloadable Flash, 512 bytes EEPROM, 512 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, flexible timer/counters with compare modes, internal and external interrupts, a programmable serial UART, programmable Watchdog Timer with internal oscillator, an SPI serial port and two software selectable power saving modes. The Idle Mode stops the CPU while allowing the SRAM, timer/counters, SPI port and interrupt system to continue functioning. The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

The device is manufactured using Atmel's high density non-volatile memory technology. The on-chip Downloadable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with Downloadable Flash on a monolithic chip, the Atmel AT90S8515 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The AT90S8515 *AVR* is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# **Pin Descriptions**

$V_{CC}$

Supply voltage

#### **GND**

Ground

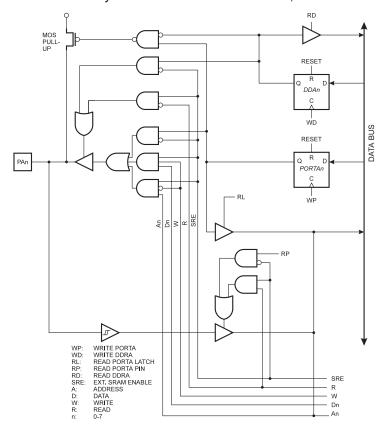

## Port A (PA7..PA0)

Port A is an 8-bit bidirectional I/O port. Port pins can provide internal pullups (selected for each bit). The Port A output buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current  $(I_{II})$  if the internal pullups are activated.

Port A serves as Multiplexed Address/Data input/output when using external SRAM.

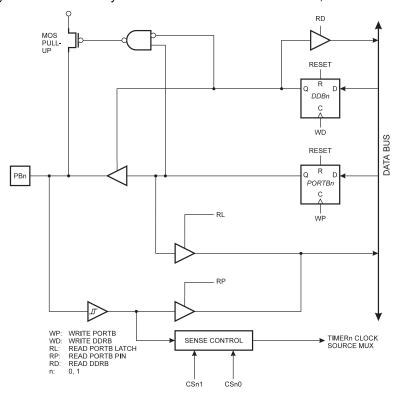

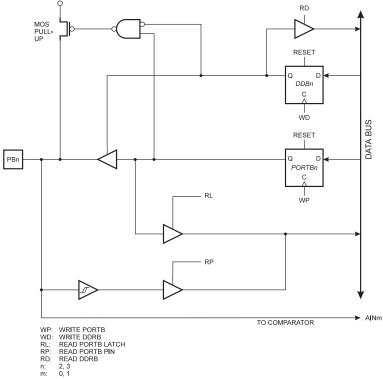

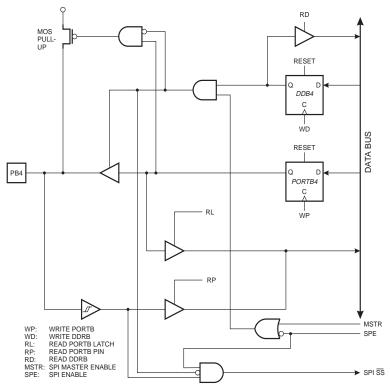

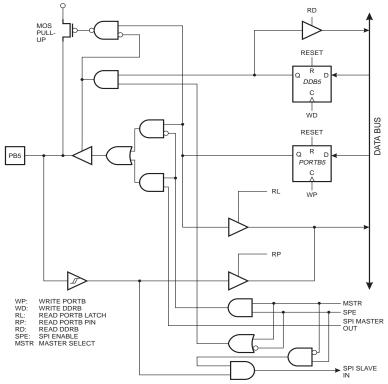

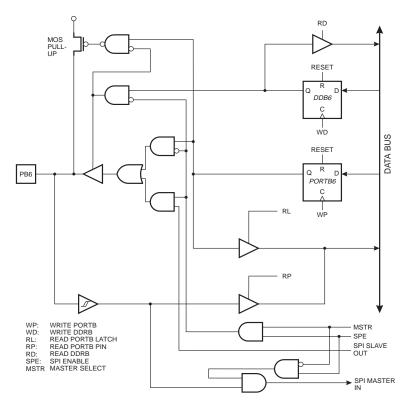

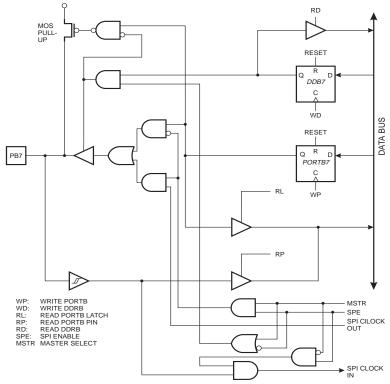

## Port B (PB7..PB0)

Port B is an 8-bit bidirectional I/O pins with internal pullups. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low will source current ( $I_{IL}$ ) if the pullups are activated.

Port B also serves the functions of various special features of the AT90S8515 as listed on Page 56.

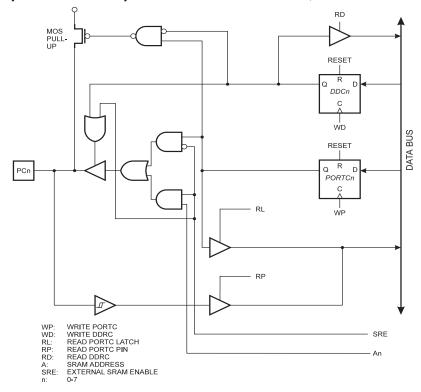

## Port C (PC7..PC0)

Port C is an 8-bit bidirectional I/O port with internal pullups. The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally pulled low will source current ( $I_{IL}$ ) if the pullups are activated.

Port C also serves as Address output when using external SRAM.

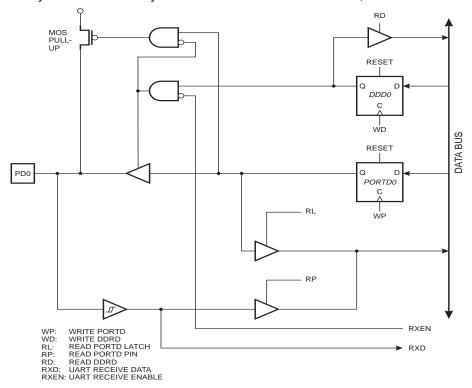

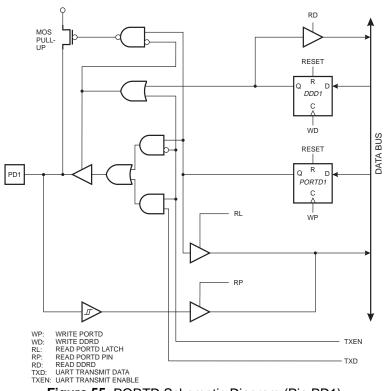

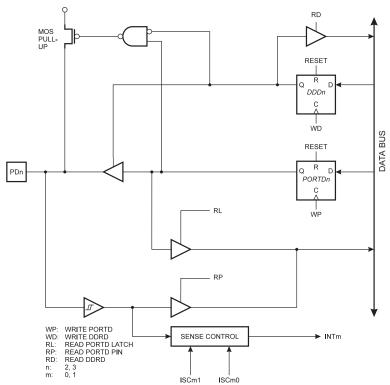

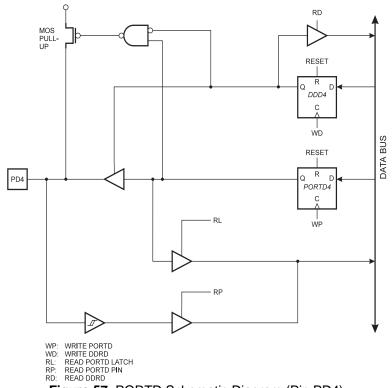

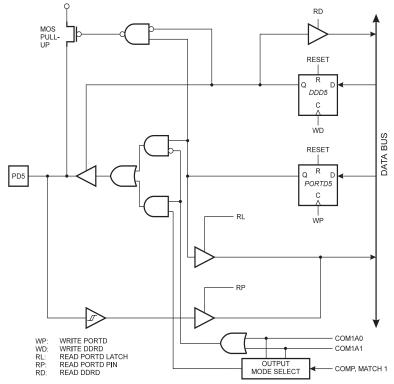

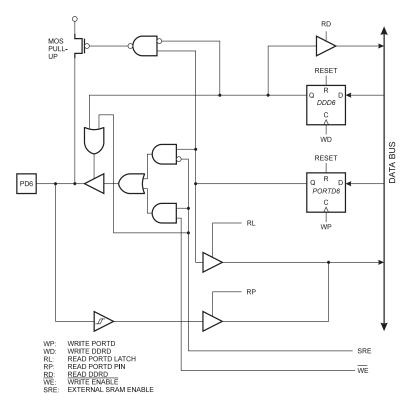

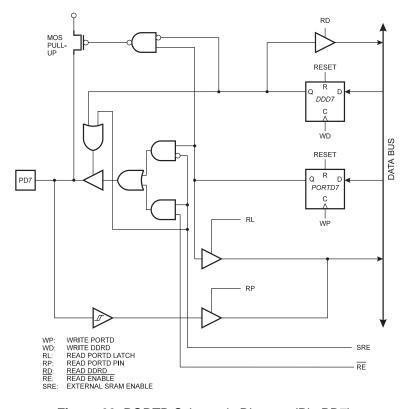

## Port D (PD7..PD0)

Port D is an 8-bit bidirectional I/O port with internal pullups. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current ( $I_{IL}$ ) if the pullups are activated.

Port D also serves the functions of various special features of the AT90S8515 as listed on Page 62.

## **RESET**

Reset input. A low on this pin for two machine cycles while the oscillator is running resets the device.

#### XTAL<sub>1</sub>

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

## XTAL2

Output from the inverting oscillator amplifier

#### **ICP**

ICP is the input pin for the Timer/Counter1 Input Capture function.

#### OC1E

OC1B is the output pin for the Timer/Counter1 Output CompareB function

## ALE

ALE is the Address Latch Enable used when the External Memory is enabled. The ALE strobe is used to latch the loworder address (8 bits) into an address latch during the first access cycle, and the AD0-7 pins are used for data during the second access cycle.

# **Crystal Oscillator**

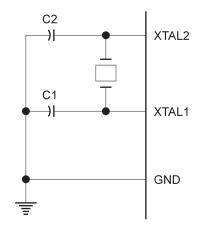

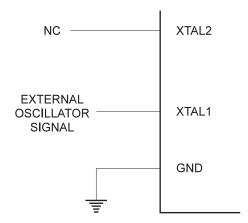

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an onchip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 3.

Figure 2. Oscillator Connections

Figure 3. External Clock Drive Configuration

## AT90S8515 Architectural Overview

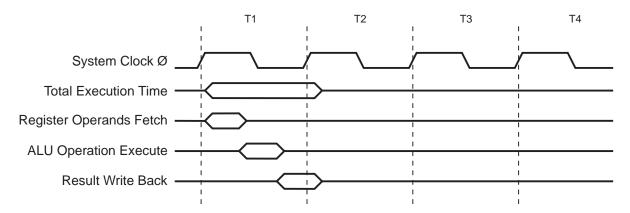

The fast-access register file concept contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock cycle, one ALU (Arithmetic Logic Unit) operation is executed. Two operands are output from the register file, the operation is executed, and the result is stored back in the register file - in one clock cycle.

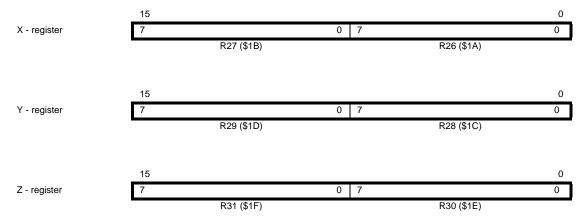

Six of the 32 registers can be used as three 16-bits indirect address register pointers for Data Space addressing - enabling efficient address calculations. One of the three address pointers is also used as the address pointer for the constant table look up function. These added function registers are the 16-bits X-register, Y-register and Z-register.

#### AVR AT90S8515 Architecture Data Bus 8-bit Program Status Control 4K X 16 Counter and Test Registrers Program Memory Interrupt 32 x 8 Unit Instruction General Purpose Register SPI Registrers Unit Instruction Decoder Serial Indirect Addressing Direct Addressing **UART** ALU Control Lines 8-bit Timer/Counter 16-bit Timer/Counter 512 x 8 with PWM Data SRAM Watchdog Timer 512 x 8 Analog **FFPROM** Comparator 32 I/O Lines

Figure 4. The AT90S8515 AVR Enhanced RISC Architecture

The ALU supports arithmetic and logic functions between registers or between a constant and a register. Single register operations are also executed in the ALU. Figure 4 shows the AT90S8515 *AVR* Enhanced RISC microcontroller architecture.

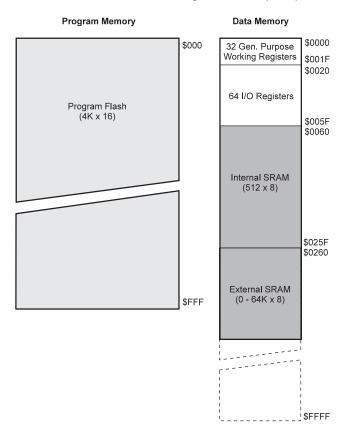

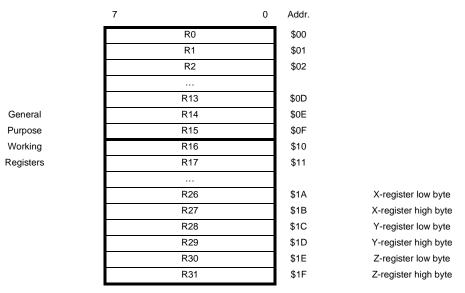

In addition to the register operation, the conventional memory addressing modes can be used on the register file as well. This is enabled by the fact that the register file is assigned the 32 lowermost Data Space addresses (\$00 - \$1F), allowing them to be accessed as though they were ordinary memory locations.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, Timer/Counters, A/D-converters, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the register file, \$20 - \$5F.

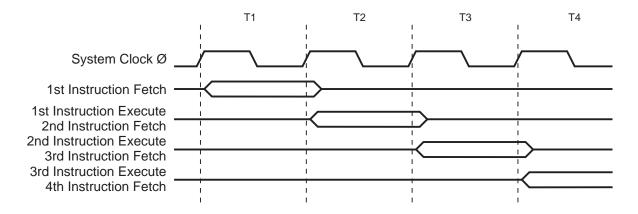

The AVR uses a Harvard architecture concept - with separate memories and buses for program and data. The program memory is executed with a single level pipelining. While one instruction is being executed, the next instruction is prefetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is in-system downloadable Flash memory.

With the relative jump and call instructions, the whole 4K address space is directly accessed. Most *AVR* instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is effectively allocated in the general data SRAM, and consequently the stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are executed). The 16-bit stack pointer SP is read/write accessible in the I/O space.

The 512 bytes data SRAM can be easily accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

Figure 5. Memory Maps

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address the higher the priority.

# The General Purpose Register File

Figure 6 shows the structure of the 32 general purpose working registers in the CPU.

Figure 6. AVR CPU General Purpose Working Registers

All the register operating instructions in the instruction set have direct and single cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI and ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file - R16..R31. The general SBC, SUB, CP, AND and OR and all other operations between two registers or on a single register apply to the entire register file.

As shown in Figure 6, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X,Y and Z registers can be set to index any register in the file.

# THE X-REGISTER, Y-REGISTER AND Z-REGISTER

The registers R26..R31 have some added functions to their general purpose usage. These registers are address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y and Z are defined as:

Figure 7. The X, Y and Z Registers

In the different addressing modes these address registers have functions as fixed displacement, automatic increment and decrement (see the descriptions for the different instructions).

# The ALU - Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories - arithmetic, logical and bit-functions.

# The Downloadable Flash Program Memory

The AT90S8515 contains 8K bytes on-chip downloadable Flash memory for program storage. Since all instructions are 16-or 32-bit words, the Flash is organized as  $4K \times 16$ . The Flash memory has an endurance of at least 1000 write/erase cycles. The AT90S8515 Program Counter (PC) is 12 bits wide, thus addressing the 4096 program memory addresses.

See Page 73 for a detailed description on Flash data downloading.

Constant tables must be allocated within the address 0-4K (see the LPM - Load Program Memory instruction description). See Page 9 for the different program memory addressing modes.

# The SRAM Data Memory - Internal and External

The following figure shows how the AT90S8515 SRAM Memory is organized:

| Register File | Data Address Space |

|---------------|--------------------|

| R0            | \$0000             |

| R1            | \$0001             |

| R2            | \$0002             |

|               |                    |

| R29           | \$001D             |

| R30           | \$001E             |

| R31           | \$001F             |

| I/O Registers |                    |

| \$00          | \$0020             |

| \$01          | \$0021             |

| \$02          | \$0022             |

|               |                    |

| \$3D          | \$005D             |

| \$3E          | \$005E             |

| \$3F          | \$005F             |

|               | Internal SRAM      |

|               | \$0060             |

|               | \$0061             |

|               |                    |

|               | \$025E             |

|               | \$025F             |

|               | External SRAM      |

|               | \$0260             |

|               | \$0261             |

|               |                    |

|               | \$FFFE             |

|               |                    |

Figure 8. SRAM Organization

\$FFFF

The lower 608 Data Memory locations address the Register file, the I/O Memory and the internal data SRAM. The first 96 locations address the Register File + I/O Memory, and the next 512 locations address the internal data SRAM. An optional external data SRAM can be placed in the same SRAM memory space. This SRAM will occupy the location following the internal SRAM and up to as much as 64K - 1, depending on SRAM size.

When the addresses accessing the data memory space exceeds the internal data SRAM locations, the external data SRAM is accessed using the same instructions as for the internal data SRAM access. When the internal data space is accessed, the read and write strobe pins (RD and  $\overline{\text{WR}}$ ) are inactive during the whole access cycle. External SRAM operation is enabled by setting the SRE bit in the MCUCR register. See Page 25 for details.

Accessing external SRAM takes one additional clock cycle per byte compared to the internal SRAM. This applies to commands LD, ST, LDS, STS, PUSH, POP. If the stack is placed in the external SRAM, interrupts, subroutine calls and returns will require two more clock cycles. When the external SRAM is used with wait state, all external SRAM access takes four clock cycles extra.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-Decrement and Indirect with Post-Increment. In the register file, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode features a 63 address locations reach from the base address given by the Y or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y and Z are decremented and incremented.

The 32 general purpose working registers, 64 I/O registers, the 512 bytes of internal data SRAM, and the 64K bytes of optional external data SRAM in the AT90S8515 are all accessible through all these addressing modes.

See the next section for a detailed description of the different addressing modes.

# The Program and Data Addressing Modes

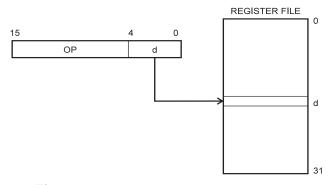

The AT90S8515 *AVR* Enhanced RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and data memory (SRAM, Register File and I/O Memory). This section describes the different addressing modes supported by the *AVR* architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

## REGISTER DIRECT, SINGLE REGISTER RD

Figure 9. Direct Single Register Addressing

The operand is contained in register d (Rd).

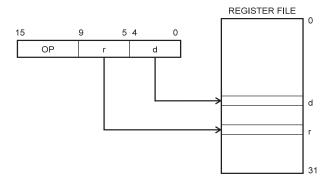

# REGISTER DIRECT, TWO REGISTERS RD AND RR

Figure 10. Direct Register Addressing, Two Registers

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

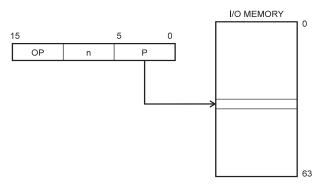

# I/O DIRECT

Figure 11. I/O Direct Addressing

Operand address is contained in 6 bits of the instruction word. n is the destination or source register address.

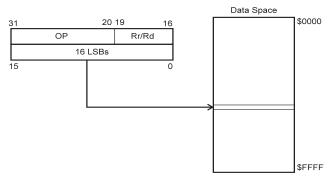

# **DATA DIRECT**

Figure 12. Direct Data Addressing

A 16-bit Data Address is contained in the 16 LSBs of a two-word instruction. Rd/Rr specify the destination or source register.

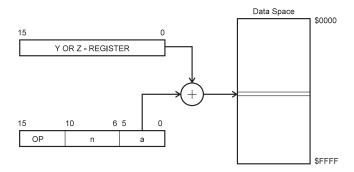

## DATA INDIRECT WITH DISPLACEMENT

Figure 13. Data Indirect with Displacement

Operand address is the result of the Y or Z-register contents added to the address contained in 6 bits of the instruction word.

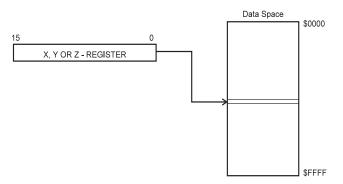

## **DATA INDIRECT**

Figure 14. Data Indirect Addressing

Operand address is the contents of the X, Y or the Z-register.

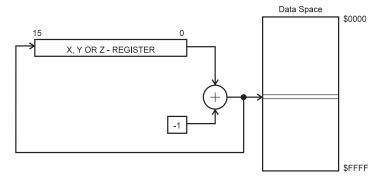

## DATA INDIRECT WITH PRE-DECREMENT

Figure 15. Data Indirect Addressing With Pre-Decrement

The X, Y or the Z-register is decremented before the operation. Operand address is the decremented contents of the X, Y or the Z-register.

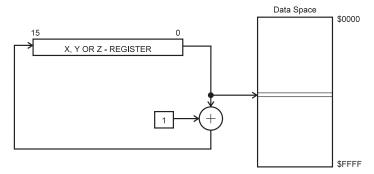

# DATA INDIRECT WITH POST-INCREMENT

Figure 16. Data Indirect Addressing With Post-Increment

The X, Y or the Z-register is incremented after the operation. Operand address is the content of the X, Y or the Z-register prior to incrementing.

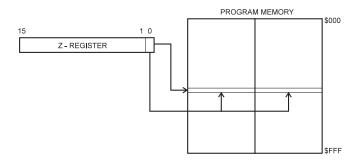

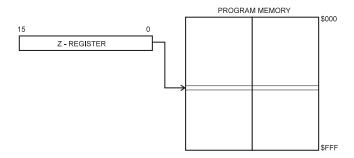

## CONSTANT ADDRESSING USING THE LPM INSTRUCTION

Figure 17. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 4K) and LSB, select low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

# INDIRECT PROGRAM ADDRESSING, IJMP AND ICALL

Figure 18. Indirect Program Memory Addressing

Program execution continues at address contained by the Z-register (i.e. the PC is loaded with the contents of the Z-register).

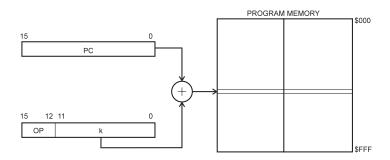

## RELATIVE PROGRAM ADDRESSING, RJMP AND RCALL

Figure 19. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

# The EEPROM Data Memory

The AT90S8515 contains 512 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on Page 38 specifying the EEPROM address registers, the EEPROM data register, and the EEPROM control register.

For the SPI data downloading, see Page 73 for a detailed description.

# **Memory Access Times and Instruction Execution Timing**

This section describes the general access timing concepts for instruction execution and internal memory access.

The AVR CPU is driven by the System Clock  $\emptyset$ , directly generated from the external clock crystal for the chip. No internal clock division is used.

Figure 20 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 20. The Parallel Instruction Fetches and Instruction Executions

Figure 21 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 21. Single Cycle ALU Operation

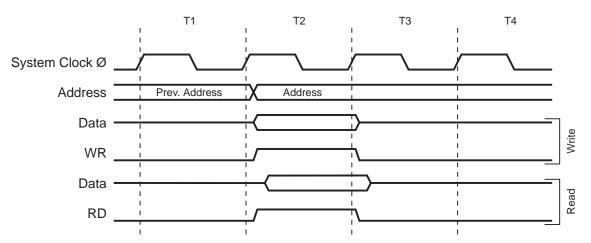

The internal data SRAM access is performed in two System Clock cycles as described in Figure 22.

Figure 22. On-Chip Data SRAM Access Cycles

The external data SRAM access is performed in two System Clock cycles as described in Figure 22.

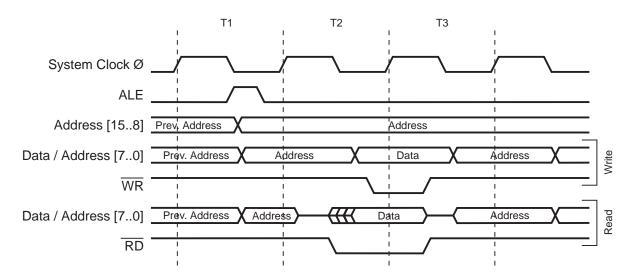

Figure 23. External Data SRAM Memory Cycles without Wait State

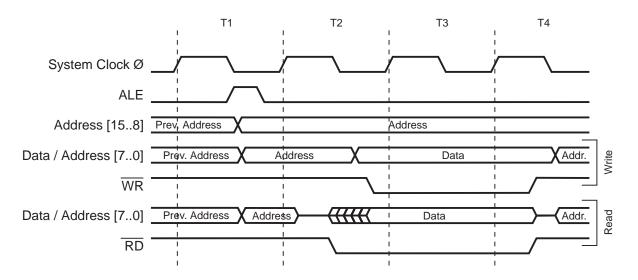

The external data SRAM memory access cycle with the Wait State bit enabled (Wait State active) is shown in Figure 24.

Figure 24. External Data SRAM Memory Cycles with Wait State

# I/O Memory

The I/O space definition of the AT90S8515 is shown in the following table:

**Table 1.** AT90S8515 I/O Space

| Address Hex | Name   | Function                                           |

|-------------|--------|----------------------------------------------------|

| \$3F (\$5F) | SREG   | Status REGister                                    |

| \$3E (\$5E) | SPH    | Stack Pointer High                                 |

| \$3D (\$5D) | SPL    | Stack Pointer Low                                  |

| \$3B (\$5B) | GIMSK  | General Interrupt MaSK register                    |

| \$3A (\$A)  | GIFR   | General Interrupt Flag Register                    |

| \$39 (\$59) | TIMSK  | Timer/Counter Interrupt MaSK register              |

| \$38 (\$58) | TIFR   | Timer/Counter Interrupt Flag register              |

| \$35 (\$55) | MCUCR  | MCU general Control Register                       |

| \$33 (\$53) | TCCR0  | Timer/Counter0 Control Register                    |

| \$32 (\$52) | TCNT0  | Timer/Counter0 (8-bit)                             |

| \$2F (\$4F) | TCCR1A | Timer/Counter1 Control Register A                  |

| \$2E (\$4E) | TCCR1B | Timer/Counter1 Control Register B                  |

| \$2D (\$4D) | TCNT1H | Timer/Counter1 High Byte                           |

| \$2C (\$4C) | TCNT1L | Timer/Counter1 Low Byte                            |

| \$2B (\$4B) | OCR1AH | Timer/Counter1 Output Compare Register A High Byte |

| \$2A (\$4A) | OCR1AL | Timer/Counter1 Output Compare Register A Low Byte  |

| \$29 (\$49) | OCR1BH | Timer/Counter1 Output Compare Register B High Byte |

| \$28 (\$48) | OCR1BL | Timer/Counter1 Output Compare Register B Low Byte  |

| \$25 (\$45) | ICR1H  | T/C 1 Input Capture Register High Byte             |

| \$24 (\$44) | ICR1L  | T/C 1 Input Capture Register Low Byte              |

| \$21 (\$41) | WDTCR  | Watchdog Timer Control Register                    |

| \$1F (\$3E) | EEARH  | EEPROM Address Register High Byte                  |

| \$1E (\$3E) | EEARL  | EEPROM Address Register Low Byte                   |

| \$1D (\$3D) | EEDR   | EEPROM Data Register                               |

| \$1C (\$3C) | EECR   | EEPROM Control Register                            |

| \$1B (\$3B) | PORTA  | Data Register, Port A                              |

| \$1A (\$3A) | DDRA   | Data Direction Register, Port A                    |

| \$19 (\$39) | PINA   | Input Pins, Port A                                 |

| \$18 (\$38) | PORTB  | Data Register, Port B                              |

| \$17 (\$37) | DDRB   | Data Direction Register, Port B                    |

| \$16 (\$36) | PINB   | Input Pins, Port B                                 |

| \$15 (\$35) | PORTC  | Data Register, Port C                              |

| \$14 (\$34) | DDRC   | Data Direction Register, Port C                    |

| \$13 (\$33) | PINC   | Input Pins, Port C                                 |

| \$12 (\$32) | PORTD  | Data Register, Port D                              |

| \$11 (\$31) | DDRD   | Data Direction Register, Port D                    |

| \$10 (\$30) | PIND   | Input Pins, Port D                                 |

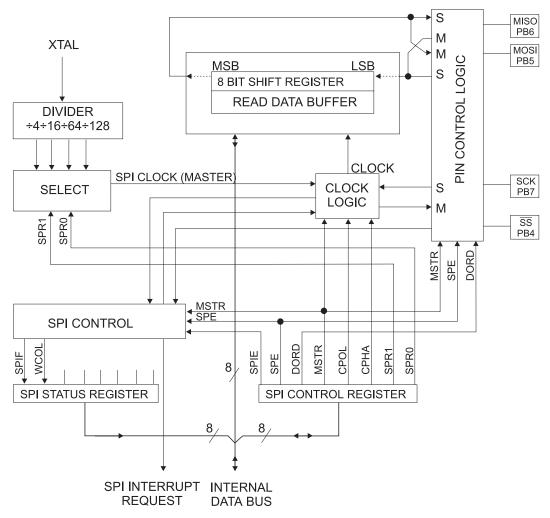

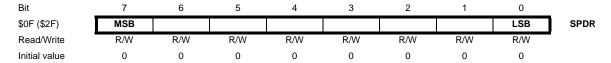

| \$0F (\$2F) | SPDR   | SPI I/O Data Register                              |

| \$0E (\$2E) | SPSR   | SPI Status Register                                |

| \$0D (\$2D) | SPCR   | SPI Control Register                               |

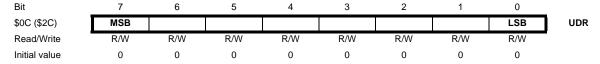

| \$0C (\$2C) | UDR    | UART I/O Data Register                             |

| \$0B (\$2B) | USR    | UART Status Register                               |

| \$0A (\$2A) | UCR    | UART Control Register                              |

| \$09 (\$29) | UBRR   | UART Baud Rate Register                            |

| \$08 (\$28) | ACSR   | Analog Comparator Control and Status Register      |

Note: reserved and unused locations are not shown in the table

All the different AT90S8515 I/Os and peripherals are placed in the I/O space. The different I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general purpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set chapter for more details.

When using the I/O specific commands, IN, OUT, SBIS and SBIC, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

The different I/O and peripherals control registers are explained in the following chapters.

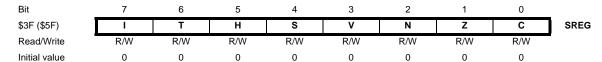

#### THE STATUS REGISTER - SREG

The AVR status register - SREG - at I/O space location \$3F (\$5F) is defined as:

#### Bit 7 - I: Global Interrupt Enable:

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in the interrupt mask registers - GIMSK and TIMSK. If the global interrupt enable register is cleared (zero), none of the interrupts are enabled independent of the GIMSK and TIMSK values. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts.

#### Bit 6 - T: Bit Copy Storage:

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T bit as source and destination for the operated bit. A bit from a register in the register file can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the register file by the BLD instruction.

#### Bit 5 - H: Half Carry Flag:

The half carry flag H indicates a half carry in some arithmetic operations. See the Instruction Set Description for detailed information.

## Bit 4 - S: Sign Bit, $S = N \oplus V$ :

The S-bit is always an exclusive or between the negative flag N and the two's complement overflow flag V. See the Instruction Set Description for detailed information.

#### Bit 3 - V: Two's Complement Overflow Flag:

The two's complement overflow flag V supports two's complement arithmetics. See the Instruction Set Description for detailed information.

#### Bit 2 - N: Negative Flag:

The negative flag N indicates a negative result after the different arithmetic and logic operations. See the Instruction Set Description for detailed information.

#### Bit 1 - Z: Zero Flag:

The zero flag Z indicates a zero result after the different arithmetic and logic operations. See the Instruction Set Description for detailed information.

## Bit 0 - C: Carry Flag:

The carry flag C indicates a carry in an arithmetic or logic operation. See the Instruction Set Description for detailed information.

#### THE STACK POINTER - SP

The general AVR 16-bit Stack Pointer is effectively built up of two 8-bit registers in the I/O space locations \$3E (\$5E) and \$3D (\$5D). As the AT90S8515 supports up to 64 kB external SRAM, all 16-bits are used.

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |     |

|---------------|------|------|------|------|------|------|-----|-----|-----|

| \$3E (\$5E)   | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 | SPH |

| \$3D (\$5D)   | SP7  | SP6  | SP5  | SP4  | SP3  | SP2  | SP1 | SP0 | SPL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   | •   |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

|               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

The Stack Pointer points to the data SRAM stack area where the Subroutine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer is decremented by one when data is pushed onto the Stack with the PUSH instruction, and it is decremented by two when data is pushed onto the Stack with subroutine CALL and interrupt. The Stack Pointer is incremented by one when data is popped from the Stack with the POP instruction, and it is incremented by two when data is popped from the Stack with return from subroutine RET or return from interrupt IRET.

# **Reset and Interrupt Handling**

The AT90S8515 provides 12 different interrupt sources. These interrupts and the separate reset vector, each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be set (one) together with the I-bit in the status register in order to enable the interrupt.

The lowest addresses in the program memory space are automatically defined as the Reset and Interrupt vectors. The complete list of vectors is shown in Table 2. The list also determines the priority levels of the different interrupts. The lower the address the higher is the priority level. RESET has the highest priority, and next is INT0 - the External Interrupt Request 0 etc.

Table 2. Reset and Interrupt Vectors

| Vector No. | Program Address | Source       | Interrupt Definition            |  |  |

|------------|-----------------|--------------|---------------------------------|--|--|

| 1          | \$000           | RESET        | Hardware Pin and Watchdog Reset |  |  |

| 2          | \$001           | INT0         | External Interrupt Request 0    |  |  |

| 3          | \$002           | INT1         | External Interrupt Request 1    |  |  |

| 4          | \$003           | TIMER1 CAPT  | Timer/Counter1 Capture Event    |  |  |

| 5          | \$004           | TIMER1 COMPA | Timer/Counter1 Compare Match A  |  |  |

| 6          | \$005           | TIMER1 COMPB | Timer/Counter1 Compare Match B  |  |  |

| 7          | \$006           | TIMER1 OVF   | Timer/Counter1 Overflow         |  |  |

| 8          | \$007           | TIMER0, OVF  | Timer/Counter0 Overflow         |  |  |

| 9          | \$008           | SPI, STC     | Serial Transfer Complete        |  |  |

| 10         | \$009           | UART, RX     | UART, Rx Complete               |  |  |

| 11         | \$00A           | UART, UDRE   | UART Data Register Empty        |  |  |

| 12         | \$00B           | UART, TX     | UART, Tx Complete               |  |  |

| 13         | \$00C           | ANA_COMP     | Analog Comparator               |  |  |

The most typical and general program setup for the Reset and Interrupt Vector Addresses are:

| Address | Labels | Code            |            | C | omments                  |

|---------|--------|-----------------|------------|---|--------------------------|

| \$000   |        | rjmp            | RESET      | ; | Reset Handle             |

| \$001   |        | rjmp            | EXT_INT0   | ; | IRQ0 Handle              |

| \$002   |        | rjmp            | EXT_INT1   | ; | IRQ1 Handle              |

| \$003   |        | rjmp            | TIM1_CAPT  | ; | Timer1 capture Handle    |

| \$004   |        | rjmp            | TIM1_COMPA | ; | Timer1 compareA Handle   |

| \$005   |        | rjmp            | TIM1_OVF   | ; | Timer1 overflow Handle   |

| \$006   |        | rjmp            | TIM1_OVF   | ; | Timer1 overflow Handle   |

| \$007   |        | rjmp            | TIMO_OVF   | ; | Timer0 overflow Handle   |

| \$008   |        | rjmp            | SPI_HANDLE | ; | SPI TX Handle            |

| \$009   |        | rjmp            | UART_RXC   | ; | UART RX Complete Handle  |

| \$00a   |        | rjmp            | UART_DRE   | ; | UDR Empty Handle         |

| \$00b   |        | rjmp            | UART_TXC   | ; | UART TX Complete Handle  |

| \$00c   |        | rjmp            | ANA_COMP   | ; | Analog Comparator Handle |

| ;       |        |                 |            |   |                          |

| \$00d   | MAIN:  | <instr></instr> | xxx        | ; | Main program start       |

|         |        |                 |            |   |                          |

## **RESET SOURCES**

The AT90S8515 has three sources of reset:

- Power-On Reset. The MCU is reset when a supply voltage is applied to the VCC and GND pins.

- External Reset. The MCU is reset when a low level is present on the RESET pin for more than two XTAL cycles

- Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

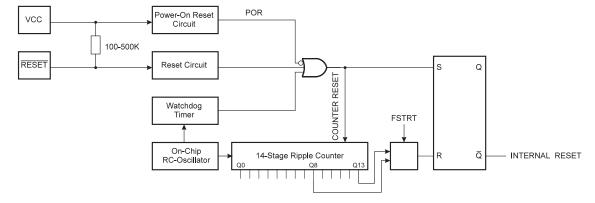

During reset, all I/O registers are then set to their initial values, and the program starts execution from address \$000. The instruction placed in address \$000 must be an RJMP - relative jump - instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can be placed at these locations. The circuit diagram in Figure 25 shows the reset logic. Table 3 defines the timing and electrical parameters of the reset circuitry.

Figure 25. Reset Logic

**Table 3**. Reset Characteristics ( $V_{CC} = 5.0V$ )

| Symbol            | Parameter                                         | Min | Тур                | Max | Units |

|-------------------|---------------------------------------------------|-----|--------------------|-----|-------|

| V <sub>POT</sub>  | Power-On Reset Threshold Voltage                  | 1.8 | 2                  | 2.2 | V     |

| V <sub>RST</sub>  | RESET Pin Threshold Voltage                       |     | V <sub>CC</sub> /2 |     | V     |

| t <sub>POR</sub>  | Power-On Reset Period                             | 2   | 3                  | 4   | ms    |

| <sup>t</sup> TOUT | Reset Delay Time-Out Period<br>FSTRT Unprogrammed | 11  | 16                 | 21  | ms    |

| t <sub>TOUT</sub> | Reset Delay Time-Out Period<br>FSTRT Programmed   | 1.0 | 1.1                | 1.2 | ms    |

#### **POWER-ON RESET**

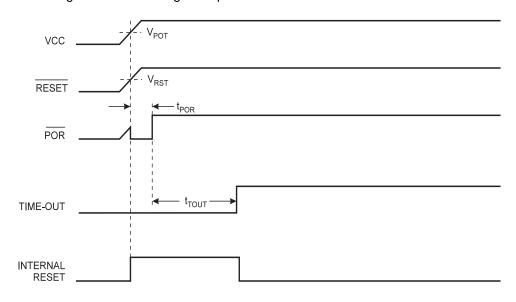

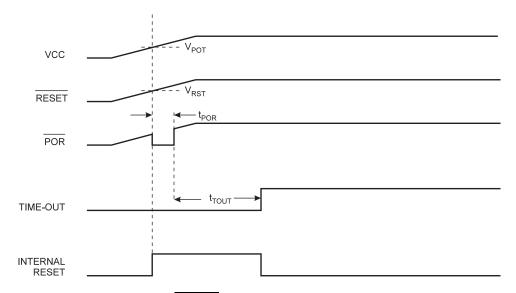

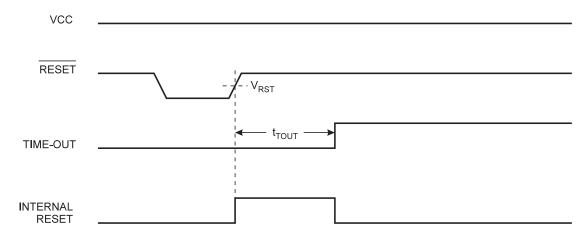

A Power-On Reset (POR) circuit ensures that the device is not started until  $V_{CC}$  has reached a safe level. As shown in Figure 25, an internal timer clocked from the Watchdog timer oscillator prevents the MCU from starting until after a certain period after  $V_{CC}$  has reached the Power-On Threshold voltage -  $V_{POT}$ , regardless of the  $V_{CC}$  rise time (see Figure 26 and Figure 27). The total reset period is the Power-On Reset period -  $t_{POR}$  + the Delay Time-out period -  $t_{TOUT}$ . The FSTRT fuse bit in the Flash can be programmed to give a shorter start-up time if a ceramic resonator or any other fast-start oscillator is used to clock the MCU.

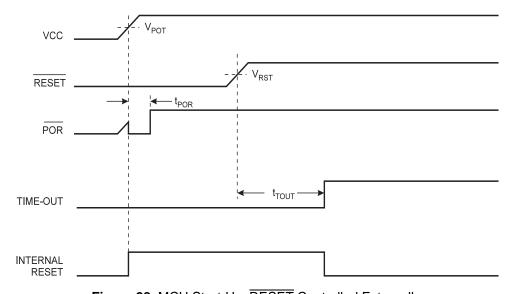

As the pin is pulled high by an on-chip resistor, the pin can be left unconnected if no external reset is required. Connecting to  $V_{CC}$  will have the same effect. By holding the pin low for a period after  $V_{CC}$  has been applied, the Power-On Reset period can be extended. Refer to Figure 28 for a timing example on this.

Figure 26. MCU Start-Up,  $\overline{\text{RESET}}$  Tied to  $V_{\text{CC}}$  or Unconnected. Rapidly Rising  $V_{\text{CC}}$

Figure 27. MCU Start-Up,  $\overline{\text{RESET}}$  Tied to  $V_{\text{CC}}$  or Unconnected. Slowly Rising  $V_{\text{CC}}$

Figure 28. MCU Start-Up, RESET Controlled Externally

#### **EXTERNAL RESET**

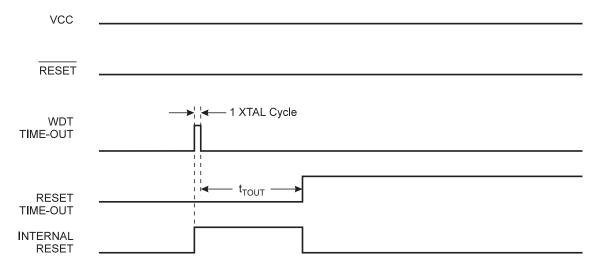

An external reset is generated by a low level on the  $\overline{RESET}$  pin. The  $\overline{RESET}$  pin must be held low for at least two crystal clock cycles. When reaches the Reset Threshold Voltage -  $V_{RST}$  on its positive edge, the delay timer starts the MCU after the Time-out period  $t_{TOUT}$  has expired.

Figure 29. External Reset During Operation

#### **WATCHDOG RESET**

When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period  $t_{TOUT}$ . Refer to Page 37 for details on operation of the Watchdog.

Figure 30. Watchdog Reset During Operation

#### INTERRUPT HANDLING

The AT90S8515 has two 8-bit Interrupt Mask control registers; GIMSK - General Interrupt Mask register and TIMSK - Timer/Counter Interrupt Mask register.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software must set (one) the I-bit to enable interrupts.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared.

#### THE GENERAL INTERRUPT MASK REGISTER - GIMSK

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |       |

|---------------|------|------|---|---|---|---|---|---|-------|

| \$3B (\$5B)   | INT1 | INT0 | - | - | - | - | - | - | GIMSK |

| Read/Write    | R/W  | R/W  | R | R | R | R | R | R |       |

| Initial value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |       |

## Bit 7 - INT1: External Interrupt Request 1 Enable:

When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is activated. The Interrupt Sense Control1 bits 1/0 (ISC11 and ISC10) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT1 pin or level sensed. Activity on the pin will cause an interrupt request even if INT1 is configured as an output. The corresponding interrupt of External Interrupt Request 1 is executed from program memory address \$002. See also "external Interrupts".

## Bit 6 - INT0: External Interrupt Request 0 Enable:

When the INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the external pin interrupt is activated. The Interrupt Sense Control0 bits 1/0 (ISC01 and ISC00) in the MCU general Control Register (MCUCR) defines whether the external interrupt is activated on rising or falling edge of the INT0 pin or level sensed. Activity on the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from program memory address \$001. See also "External Interrupts."

#### Bits 5..0 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and always read as zero.

## The General Interrupt FLAG Register - GIFR

| Bit           | 7     | 6     | 5 | 4 | 3 | 2 | 1 | . 0 |       |

|---------------|-------|-------|---|---|---|---|---|-----|-------|

| \$3A (\$5A)   | INTF1 | INTF0 | • | - | - | - | - | -   | GIMSK |

| Read/Write    | R/W   | R/W   | R | R | R | R | R | R   |       |

| Initial value | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0   |       |

#### Bit 7 - INTF1: External Interrupt Flag1:

When an event on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in GIMSK are set (one), the MCU will jump to the interrupt vector at address \$002. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it.

## Bit 6 - INTF0: External Interrupt Flag0:

When an event on the INT0 pin triggers an interrupt request, INTF0 becomes set (one). If the I-bit in SREG and the INT0 bit in GIMSK are set (one), the MCU will jump to the interrupt vector at address \$001. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it.

#### Bits 5..0 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and always read as zero.

#### THE TIMER/COUNTER INTERRUPT MASK REGISTER - TIMSK

| Bit           | 7     | 6      | 5      | 4 | 3      | 2 | 1     | 0 |       |

|---------------|-------|--------|--------|---|--------|---|-------|---|-------|

| \$39 (\$59)   | TOIE1 | OCIE1A | OCIE1B | - | TICIE1 | - | TOIE0 |   | TIMSK |

| Read/Write    | R/W   | R/W    | R/W    | R | R/W    | R | R/W   | R |       |

| Initial value | 0     | 0      | 0      | 0 | 0      | 0 | 0     | 0 |       |

#### Bit 7 - TOIE1: Timer/Counter1 Overflow Interrupt Enable:

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt (at vector \$006) is executed if an overflow in Timer/Counter1 occurs. The Overflow Flag (Timer/Counter1) is set (one) in the Timer/Counter Interrupt Flag Register - TIFR. When Timer/Counter1 is in PWM mode, the Timer Overflow flag is set when the counter changes counting direction at \$0000.

## Bit 6 - OCE1A :Timer/Counter1 Output CompareA Match Interrupt Enable:

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if a CompareA match in Timer/Counter1 occurs. The CompareA Flag in Timer/Counter1 is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

## Bit 5 - OCIE1B :Timer/Counter1 Output CompareB Match Interrupt Enable:

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match interrupt is enabled. The corresponding interrupt (at vector \$005) is executed if a CompareB match in Timer/Counter1 occurs. The CompareB Flag in Timer/Counter1 is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

## Bit 4 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

## Bit 3 - TICIE1: Timer/Counter1 Input Capture Interrupt Enable:

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Input Capture Event Interrupt is enabled. The corresponding interrupt (at vector \$003) is executed if a capture-triggering event occurs on pin 31, ICP. The Input Capture Flag in Timer/Counter1 is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

#### Bit 2 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

#### Bit 1 - TOIE0: Timer/Counter0 Overflow Interrupt Enable:

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$008) is executed if an overflow in Timer/Counter0 occurs. The Overflow Flag (Timer0) is set (one) in the Timer/Counter Interrupt Flag Register - TIFR.

## Bit 0 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

# THE TIMER/COUNTER INTERRUPT FLAG REGISTER - TIFR

| Bit           | 7    | 6     | 5     | 4 | 3    | 2 | 1    | 0 |      |

|---------------|------|-------|-------|---|------|---|------|---|------|

| \$38 (\$58)   | TOV1 | OCF1A | OCIFB | - | ICF1 | - | TOV0 | - | TIFR |

| Read/Write    | R/W  | R/W   | R/W   | R | R/W  | R | R/W  | R | •    |

| Initial value | 0    | 0     | 0     | 0 | 0    | 0 | 0    | 0 |      |

## Bit 7 - TOV1: Timer/Counter1 Overflow Flag:

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logic one to the flag. When the I-bit in SREG, and TOIE1 (Timer/Counter1 Overflow Interrupt Enable), and TOV1 are set (one), the Timer/Counter1 Overflow Interrupt is executed. In PWM mode, this bit is set when Timer/Counter1 changes counting direction at \$0000.

# Bit 6 - OCF1A: Output Compare Flag 1A:

The OCF1A bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1A - Output Compare Register 1A. OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1A (Timer/Counter1 Compare match InterruptA Enable), and the OCF1A are set (one), the Timer/Counter1 Compare match Interrupt is executed.

#### Bit 5 - OCF1B: Output Compare Flag 1B:

The OCF1B bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1B - Output Compare Register 1B. OCF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1 is cleared by writing a logic one to the flag.. When the I-bit in SREG, and OCIE1B (Timer/Counter1 Compare match InterruptB Enable), and the OCF1B are set (one), the Timer/Counter1 Compare match Interrupt is executed.

## Bit 4 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

#### Bit 3 - ICF1: - Input Capture Flag 1:

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register - ICR1. ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logic one to the flag.

## Bit 2 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

## Bit 1 - TOV0: Timer/Counter0 Overflow Flag:

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

## Bit 0 - Res: Reserved bit:

This bit is a reserved bit in the AT90S8515 and always reads zero.

## external Interrupts

The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register - MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register - MCUCR.

#### INTERRUPT RESPONSE TIME

The interrupt execution response for all the enabled *AVR* interrupts is 4 clock cycles minimum. After the 4 clock cycles the program vector address for the actual interrupt handling routine is executed. During this 4 clock cycle period, the Program Counter (2 bytes) is pushed onto the Stack, and the Stack Pointer is decremented by 2. The vector is a relative jump to the interrupt routine, and this jump takes 2 clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes 4 clock cycles. During these 4 clock cycles, the Program Counter (2 bytes) is popped back from the Stack, and the Stack Pointer is incremented by 2. When AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register - SREG - is not handled by the *AVR* hardware, neither for interrupts nor for subroutines. For the interrupt handling routines requiring a storage of the SREG, this must be performed by user software.

For Interrupts triggered by events that can remain static (E.g. the Output Compare Register1 A matching the value of Timer/Counter1) the interrupt flag is set when the event occurs. If the interrupt flag is cleared and the interrupt condition persists, the flag will not be set until the event occurs the next time.

## **MCU CONTROL REGISTER - MCUCR**

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|---------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55)   | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write    | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| Initial value | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

## Bit 7 - SRE: External SRAM Enable:

When the SRE bit is set (one), the external data SRAM is enabled, and the pin functions AD0-7 (Port A), A8-15 (Port C), WR and RD (Port D) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See "The SRAM Data Memory - Internal and External" for description of the External SRAM pin functions. When the SRE bit is cleared (zero), the external data SRAM is disabled, and the normal pin and data direction settings are used.

#### Bit 6 - SRW: External SRAM Wait State:

When the SRW bit is set (one), a one cycle wait state is inserted in the external data SRAM access cycle. When the SRW bit is cleared (zero), the external data SRAM access is executed with the normal two cycle scheme. See Figure 23 External Data SRAM Memory Cycles without Wait State and Figure 24: External Data SRAM Memory Cycles with Wait State.

#### Bit 5 - SE: Sleep Enable:

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just before the execution of the SLEEP instruction.

## Bit 4 - SM : Sleep Mode:

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle Mode is selected as Sleep Mode. When SM is set (one), Power Down mode is selected as sleep mode. For details, refer to the paragraph "Sleep Modes" below.

## Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 bit 1 and bit 0:

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corresponding interrupt mask in the GIMSK is set. The level and edges on the external INT1 pin that activate the interrupt are defined in the following table:

Table 4. Interrupt 1 Sense Control

| ISC11 | ISC10 | Description                                              |  |  |  |

|-------|-------|----------------------------------------------------------|--|--|--|

| 0     | 0     | The low level of INT1 generates an interrupt request.    |  |  |  |

| 0     | 1     | Reserved                                                 |  |  |  |

| 1     | 0     | The falling edge of INT1 generates an interrupt request. |  |  |  |

| 1     | 1     | The rising edge of INT1 generates an interrupt request.  |  |  |  |

Note:

When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

# Bit 1, 0 - ISC01, ISC00: Interrupt Sense Control 0 bit 1 and bit 0:

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask is set. The level and edges on the external INT0 pin that activate the interrupt are defined in the following table:

Table 5. Interrupt 0 Sense Control

| ISC01 | ISC00 | Description                                              |  |  |  |  |

|-------|-------|----------------------------------------------------------|--|--|--|--|

| 0     | 0     | ne low level of INT0 generates an interrupt request.     |  |  |  |  |

| 0     | 1     | Reserved                                                 |  |  |  |  |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |  |  |  |  |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |  |  |  |  |

Note:

When changing the ISC10/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

## Sleep Modes

To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset vector.

Note that if a *level* triggered interrupt is used for wake-up from power down, the low level must be held for a time longer than the oscillator start-up time of 16 ms. Otherwise, the interrupt flag may return to zero before the MCU starts executing.

#### **IDLE MODE**

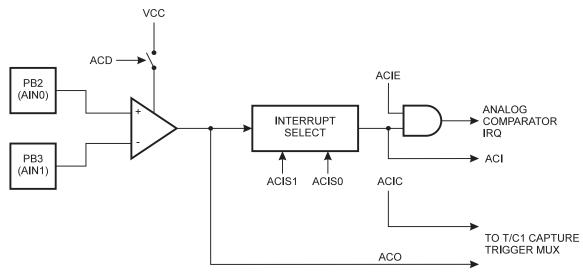

When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and watchdog reset. If wakeup from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status register - ACSR. This will reduce power consumption during Idle Mode.

#### **POWER DOWN MODE**

When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power Down Mode. In this mode, the external oscillator is stopped. The user can select whether the watchdog shall be enabled during power-down mode. If the watchdog is enabled, it will wake up the MCU when the Watchdog Time-out period expires. If the watchdog is disabled, only an external reset or an external level triggered interrupt can wake up the MCU.

# **Timer / Counters**

The AT90S8515 provides two general purpose Timer/Counters - one 8-bit T/C and one 16-bit T/C. The Timer/Counters have individual prescaling selection from the same 10-bit prescaling timer. Both Timer/Counters can either be used as a timer with an internal clock timebase or as a counter with an external pin connection which triggers the counting.

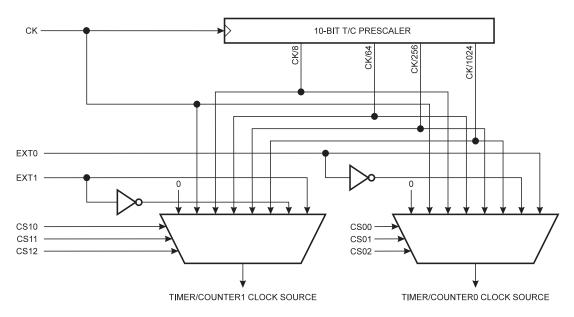

## The Timer/Counter Prescaler

Figure 31 shows the general Timer/Counter prescaler.

Figure 31. Timer/Counter Prescaler

The four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024 where CK is the oscillator clock. For the two Timer/Counters, added selections as CK, external source and stop, can be selected as clock sources.

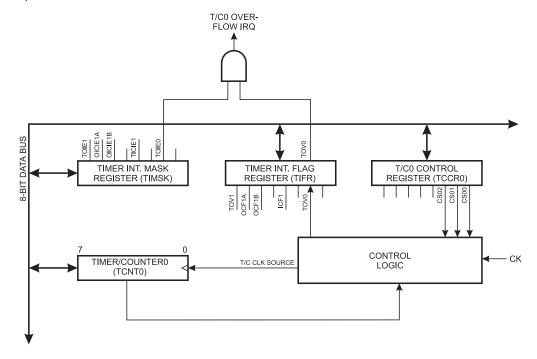

## The 8-Bit Timer/Counter0

Figure 32 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK, or an external pin. In addition it can be stopped as described in the specification for the Timer/Counter0 Control Register - TCCR0. The overflow status flag is found in the Timer/Counter Insterrupt Flag Register - TIFR. Control signals are found in the Timer/Counter0 Control Register - TCCR0. The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register - TIMSK.

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high resolution and a high accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

Figure 32. Timer/Counter0 Block Diagram

## THE TIMER/COUNTERO CONTROL REGISTER - TCCRO

| Bit           | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|---------------|---|---|---|---|---|------|------|------|-------|

| \$33 (\$53)   | - | - | - | - | - | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write    | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### Bits 7.6 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and always read zero.

## Bits 2,1,0 - CS02, CS01, CS00: Clock Select0, bit 2,1 and 0:

The Clock Select0 bits 2,1 and 0 define the prescaling source of Timer0.

Table 6. Clock 0 Prescale Select

| CS02 | CS01 | CS00 | Description                          |  |

|------|------|------|--------------------------------------|--|

| 0    | 0    | 0    | Stop, the Timer/Counter0 is stopped. |  |

| 0    | 0    | 1    | К                                    |  |

| 0    | 1    | 0    | CK/8                                 |  |

| 0    | 1    | 1    | CK / 64                              |  |

| 1    | 0    | 0    | CK / 256                             |  |

| 1    | 0    | 1    | CK / 1024                            |  |

| 1    | 1    | 0    | External Pin T0, falling edge        |  |

| 1    | 1    | 1    | External Pin T0, rising edge         |  |

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used, the corresponding setup must be performed in the actual data direction control register (cleared to zero gives an input pin).

## THE TIMER COUNTER 0 - TCNT0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |       |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| \$32 (\$52)   | MSB |     |     |     |     |     |     | LSB | TCNT0 |

| Read/Write    | R/W | •     |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |       |

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the clock cycle following the write operation.

## The 16-Bit Timer/Counter1

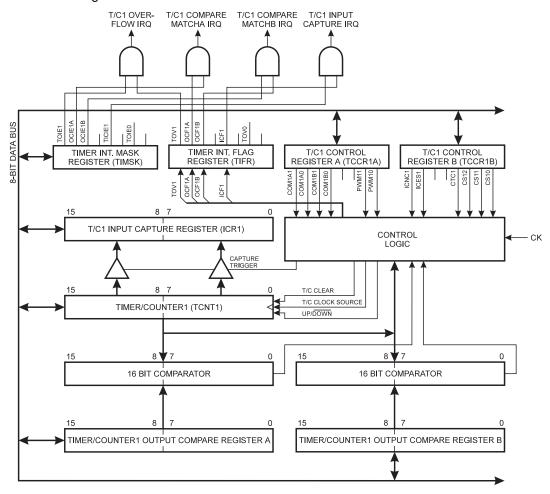

Figure 33 shows the block diagram for Timer/Counter1.

Figure 33. Timer/Counter1 Block Diagram

The 16-bit Timer/Counter1 can select clock source from CK, prescaled CK, or an external pin. In addition it can be stopped as described in the specification for the Timer/Counter1 Control Registers - TCCR1A and TCCR1B. The different status flags (overflow, compare match and capture event) and control signals are found in the Timer/Counter1 Control Registers - TCCR1A and TCCR1B. The interrupt enable/disable settings for Timer/Counter1 are found in the Timer/Counter Interrupt Mask Register - TIMSK.

When Timer/Counter1 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 16-bit Timer/Counter1 features both a high resolution and a high accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities makes the Timer/Counter1 useful for lower speed functions or exact timing functions with infrequent actions.

The Timer/Counter1 supports two Output Compare functions using the Output Compare Register 1 A and B - OCR1A and OCR1B as the data sources to be compared to the Timer/Counter1 contents. The Output Compare functions include optional clearing of the counter on compareA match, and actions on the Output Compare pins on both compare matches.

Timer/Counter1 can also be used as a 8, 9 or 10-bit Pulse With Modulator. In this mode the counter and the OCR1A/ OCR1B registers serve as a dual glitch-free stand-alone PWM with centered pulses. Refer to Page 35 for a detailed description on this function.

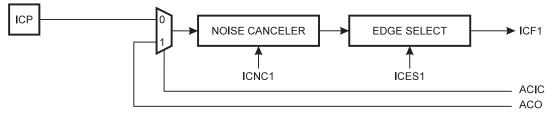

The Input Capture function of Timer/Counter1 provides a capture of the Timer/Counter1 contents to the Input Capture Register - ICR1, triggered by an external event on the Input Capture Pin - ICP. The actual capture event settings are defined by the Timer/Counter1 Control Register - TCCR1B. In addition, the Analog Comparator can be set to trigger the Input Capture. Refer to the section, "The Analog Comparator", for details on this. The ICP pin logic is shown in Figure 34.

ACIC: COMPARATOR IC ENABLE ACO: COMPARATOR OUTPUT

Figure 34. ICP Pin Schematic Diagram

The Timer/Counter1 input capture noise canceler block diagram is shown in Figure 35.

Figure 35. The Input Capture Noise Canceler

If the noise canceler function is enabled, the actual trigger condition for the capture event is monitored over 4 samples before the capture is activated. The input pin signal is sampled at XTAL clock frequency.

#### THE TIMER/COUNTER1 CONTROL REGISTER A - TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     |        |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| Initial value | 0      | 0      | 0      | Λ      | 0 | 0 | 0     | 0     |        |

## Bits 7,6 - COM1A1, COM1A0: Compare Output Mode1A, bits 1 and 0:

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1A - Output CompareA pin 1. Since this is an alternative function to an I/O port, the corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in Table 7.

## Bits 5,4 - COM1B1, COM1B0: Compare Output Mode1B, bits 1 and 0:

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in Timer/Counter1. Any output pin actions affect pin OC1B - Output CompareB. Since this is an alternative function to an I/O port, the corresponding direction control bit must be set (one) to control an output pin. The following control configuration is given:

Table 7. Compare 1 Mode Select

| COM1X1 | COM1X0 | Description                                    |  |  |  |

|--------|--------|------------------------------------------------|--|--|--|

| 0      | 0      | mer/Counter1 disconnected from output pin OC1X |  |  |  |

| 0      | 1      | Toggle the OC1X output line.                   |  |  |  |

| 1      | 0      | Clear the OC1X output line (to zero).          |  |  |  |

| 1      | 1      | Set the OC1X output line (to one).             |  |  |  |

#### X = A or B

In PWM mode, these bits have a different function. Refer to Table 11 for a detailed description.

When changing the COM1X1/COM1X0 bits, Output Compare Interrupts 1 must be disabled by clearing their Interrupt Enable bits in the TIMSK Register. Otherwise an interrupt can occur when the bits are changed.

#### Bits 3..2 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and always read zero.

#### Bits 1..0 - PWM11, PWM10: Pulse Width Modulator Select Bits:

These bits select PWM operation of Timer/Counter1 as specified in Table 8. This mode is described on Page 35.

Table 8. PWM Mode Select

| PWM11 | PWM10 | Description                                 |  |  |  |

|-------|-------|---------------------------------------------|--|--|--|

| 0     | 0     | PWM operation of Timer/Counter1 is disabled |  |  |  |

| 0     | 1     | Timer/Counter1 is an 8-bit PWM              |  |  |  |

| 1     | 0     | Timer/Counter1 is a 9-bit PWM               |  |  |  |

| 1     | 1     | Timer/Counter1 is a 10-bit PWM              |  |  |  |

## THE TIMER/COUNTER1 CONTROL REGISTER B - TCCR1B

| Bit           | 7     | 6     | 5 | 4 | 3    | 2    | 1    | 0    |        |

|---------------|-------|-------|---|---|------|------|------|------|--------|

| \$2E (\$4E)   | ICNC1 | ICES1 |   | - | CTC1 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R | R/w  | R/W  | R/W  | R/W  | _      |

| Initial value | 0     | 0     | 0 | 0 | 0    | 0    | 0    | 0    |        |

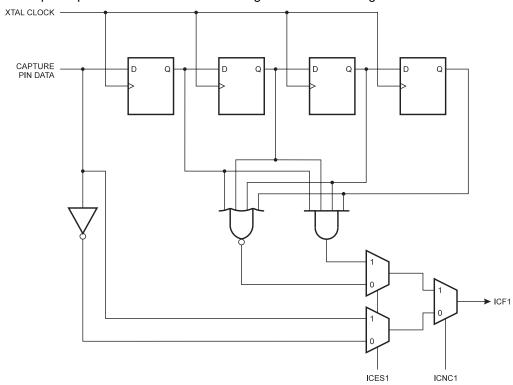

## Bit 7 - ICNC1: Input Capture1 Noise Canceler (4 CKs):

When the ICNC1 bit is cleared (zero), the input capture trigger noise canceler function is disabled. The input capture is triggered at the first rising/falling edge sampled on the ICP - input capture pin - as specified. When the ICNC1 bit is set (one), four successive samples are measures on the ICP - input capture pin, and all samples must be high/low according to the input capture trigger specification in the ICES1 bit. The actual sampling frequency is XTAL clock frequency.

# Bit 6 - ICES1: Input Capture1 Edge Select:

While the ICES1 bit is cleared (zero), the Timer/Counter1 contents are transferred to the Input Capture Register - ICR1 - on the falling edge of the input capture pin - ICP. While the ICES1 bit is set (one), the Timer/Counter1 contents are transferred to the Input Capture Register - ICR1 - on the rising edge of the input capture pin - ICP.

## Bits 5, 4 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and always read zero.

#### Bit 3 - CTC1: Clear Timer/Counter1 on Compare match:

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compareA match. If the CTC1 control bit is cleared, the Timer/Counter1 continues counting until it is stopped, cleared, wraps around (overflow) or changes direction. In PWM mode, this bit has no effect.

#### Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0:

The Clock Select1 bits 2,1 and 0 define the prescaling source of Timer/Counter1.

Table 9. Clock 1 Prescale Select

| CS12 | CS11 | CS10 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter1 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK / 64                              |

| 1    | 0    | 0    | CK / 256                             |

| 1    | 0    | 1    | CK / 1024                            |

| 1    | 1    | 0    | External Pin T1, falling edge        |

| 1    | 1    | 1    | External Pin T1, rising edge         |

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK oscillator clock. If the external pin modes are used, the corresponding setup must be performed in the actual direction control register (cleared to zero gives an input pin).

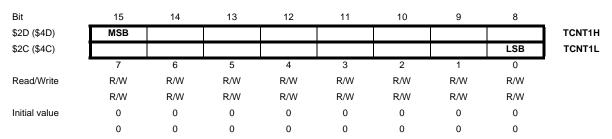

#### THE TIMER/COUNTER1 - TCNT1H AND TCNT1L

This 16-bit register contains the prescaled value of the 16-bit Timer/Counter1. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary register (TEMP).

## • TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the written data is placed in the TEMP register. Next, when the CPU writes the low byte TCNT1L, this byte of data is combined with the byte data in the TEMP register, and all 16 bits are written to the TCNT1 Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must be accessed first for a full 16-bit register write operation.

#### TCNT1 Timer/Counter1 Read:

When the CPU reads the low byte TCNT1L, the data of the low byte TCNT1L is sent to the CPU and the data of the high byte TCNT1H is placed in the TEMP register. When the CPU reads the data in the high byte TCNT1H, the CPU receives the data in the TEMP register. Consequently, the low byte TCNT1L must be accessed first for a full 16-bit register read operation.

The Timer/Counter1 is realized as an up or up/down (in PWM mode) counter with read and write access. If Timer/Counter1 is written to and a clock source is selected, the Timer/Counter1 continues counting in the timer clock cycle after it is preset with the written value.

## TIMER/COUNTER1 OUTPUT COMPARE REGISTER - OCR1AH AND OCR1AL

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |        |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$2B (\$4B)   | MSB |     |     |     |     |     |     |     | OCR1AH |

| \$2A (\$4A)   |     |     |     |     |     |     |     | LSB | OCR1AL |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

| Read/Write    | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

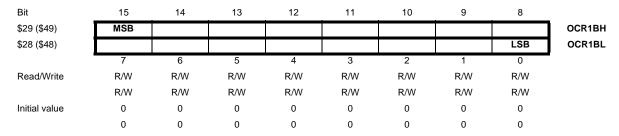

## TIMER/COUNTER1 OUTPUT COMPARE REGISTER - OCR1BH AND OCR1BL

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare Registers contain the data to be continuously compared with Timer/Counter1. Actions on compare matches are specified in the Timer/Counter1 Control and Status register.

Since the Output Compare Registers - OCR1A and OCR1B - are 16-bit registers, a temporary register TEMP is used when OCR1A/B are written to ensure that both bytes are updated simultaneously. When the CPU writes the high byte, OCR1AH or OCR1BH, the data is temporarily stored in the TEMP register. When the CPU writes the low byte, OCR1AL or OCR1BL, the TEMP register is simultaneously written to OCR1AH or OCR1BH. Consequently, the high byte OCR1AH or OCR1BH must be written first for a full 16-bit register write operation.

#### THE TIMER/COUNTER1 INPUT CAPTURE REGISTER - ICR1H AND ICR1L

| Bit           | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8   |       |

|---------------|-----|----|----|----|----|----|---|-----|-------|

| \$25 (\$45)   | MSB |    |    |    |    |    |   |     | ICR1H |

| \$24 (\$44)   |     |    |    |    |    |    |   | LSB | ICR1L |

|               | 7   | 6  | 5  | 4  | 3  | 2  | 1 | 0   |       |

| Read/Write    | R   | R  | R  | R  | R  | R  | R | R   |       |

|               | R   | R  | R  | R  | R  | R  | R | R   |       |

| Initial value | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

|               | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0   |       |

The input capture register is a 16-bit read-only register.

When the rising or falling edge (according to the input capture edge setting - ICES1) of the signal at the input capture pin - ICP - is detected, the current value of the Timer/Counter1 is transferred to the Input Capture Register - ICR1. At the same time, the input capture flag - ICF1 - is set (one).

Since the Input Capture Register - ICR1 - is a 16-bit register, a temporary register TEMP is used when ICR1 is read to ensure that both bytes are read simultaneously. When the CPU reads the low byte ICR1L, the data is sent to the CPU and the data of the high byte ICR1H is placed in the TEMP register. When the CPU reads the data in the high byte ICR1H, the CPU receives the data in the TEMP register. Consequently, the low byte ICR1L must be accessed first for a full 16-bit register read operation.

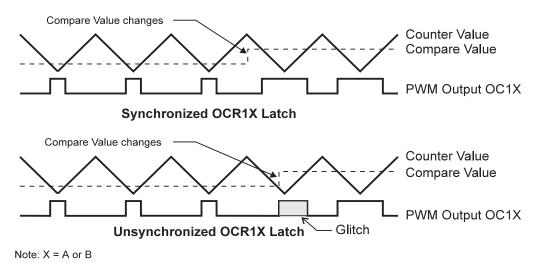

#### TIMER/COUNTER1 IN PWM MODE

When the PWM mode is selected, Timer/Counter1 and the Output Compare Register1A - OCR1A and the Output Compare Register1B - OCR1B, form a dual 8, 9 or 10-bit, free-running, glitch-free and phase correct PWM with outputs on the PD5(OC1A) and OC1B pins. Timer/Counter1 acts as an up/down counter, counting up from \$0000 to TOP (see Table 10), when it turns and counts down again to zero before the cycle is repeated. When the counter value matches the contents of the 10 least significant bits of OCR1A or OCR1B, the PD5(OC1A)/OC1B pins are set or cleared according to the settings of the COM1A1/COM1A0 or COM1B1/COM1B0 bits in the Timer/Counter1 Control Register TCCR1A. Refer to Table 11 for details.

Table 10. Timer TOP Values and PWM Frequency

| PWM<br>Resolution | Timer TOP value | Frequency              |

|-------------------|-----------------|------------------------|

| 8-bit             | \$00FF (255)    | f <sub>TC1</sub> /510  |

| 9-bit             | \$01FF (511)    | f <sub>TC1</sub> /1022 |

| 10-bit            | \$03FF(1023)    | f <sub>TC1</sub> /2046 |

Table 11. Compare1 Mode Select in PWM Mode

| COM1X1 | COM1X0 | Effect on OCX1                                                                               |  |

|--------|--------|----------------------------------------------------------------------------------------------|--|

| 0      | 0      | Not connected                                                                                |  |

| 0      | 1      | Not connected                                                                                |  |

| 1      | 0      | Cleared on compare match, upcounting. Set on compare match, downcounting (non-inverted PWM). |  |

| 1      | 1      | Cleared on compare match, downcounting. Set on compare match, upcounting (inverted PWM).     |  |

Note: X = A or B

Note that in the PWM mode, the 10 least significant OCR1A/OCR1B bits, when written, are transferred to a temporary location. They are latched when Timer/Counter1 reaches the value TOP. This prevents the occurrence of odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A/OCR1B write. See Figure 36 for an example.

Figure 36. Effects on Unsynchronized OCR1 Latching

When OCR1 contains \$0000 or TOP, the output OC1A/OC1B is held low or high according to the settings of COM1A1/COM1A0 or COM1B1/COM1B0. This is shown in Table 12:

Table 12. PWM Outputs OCR1X = \$0000 or TOP

| COM1X1 | COM1X0 | OCR1X  | Output OC1X |

|--------|--------|--------|-------------|

| 1      | 0      | \$0000 | L           |

| 1      | 0      | TOP    | Н           |

| 1      | 1      | \$0000 | Н           |

| 1      | 1      | TOP    | L           |

Note: X = A or B

In PWM mode, the Timer Overflow Flag1, TOV1, is set when the counter changes direction at \$0000. Timer Overflow Interrupt1 operates exactly as in normal Timer/Counter mode, i.e. it is executed when TOV1 is set provided that Timer Overflow Interrupt1 and global interrupts are enabled. This does also apply to the Timer Output Compare1 flags and interrupts.

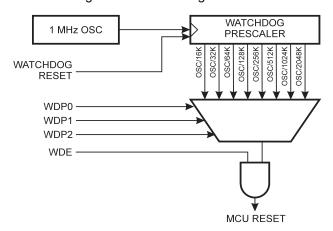

## The Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator which runs at 1MHz This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted from 16 to 2048 ms. The WDR - Watchdog Reset - instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S8515 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to Page 22.

To prevent unintentional disabling of the watchdog, a special turn-off secuence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Regiter for details

Figure 37. Watchdog Timer

#### THE WATCHDOG TIMER CONTROL REGISTER - WDTCR

| Bit           | 7 | 6 | 5 | 4      | 3   | 2    | 1    | 0    |       |

|---------------|---|---|---|--------|-----|------|------|------|-------|

| \$21 (\$41)   | - | - | - | WDTTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R/W    | R/W | R/W  | R/W  | R/W  | _     |

| Initial value | 0 | 0 | 0 | 0      | 0   | 0    | 0    | 0    |       |

#### Bits 7..5 - Res: Reserved bits:

These bits are reserved bits in the AT90S8515 and will always read as zero.

### Bit 4 - WDTOE: Watch Dog Turn-Off Enable:

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

#### Bit 3 - WDE: Watch Dog Enable: