## **DAC667**

# Microprocessor-Compatible 12-BIT DIGITAL-TO-ANALOG CONVERTER

#### **FEATURES**

- ±3/4LSB MAX NONLINEARITY OVER TEMPERATURE

- MONOTONICITY GUARANTEED OVER TEMPERATURE

- MICROCOMPUTER INTERFACE: Double-Buffered Latch

- VOLTAGE OUTPUT: ±10V, ±5V, +10V With ±12V to ±15V Supplies

- LOW POWER DISSIPATION: 345mW typ

- PIN COMPATIBLE WITH AD667

#### DESCRIPTION

The DAC667 is a complete monolithic integrated circuit microprocessor-compatible 12-bit digital-to-analog converter. It includes a precision voltage reference, microcomputer interface logic, double-buffered latch, and a 12-bit D/A converter with a voltage output amplifier. Fast current switches and a laser-trimmed thin-film resistor network provide a highly accurate and fast D/A converter.

A double-buffered latch facilitates microcomputer interfacing to 4-, 8-, 12-, or 16-bit data buses. The input buffer latch holds the 12-bit data until it is transferred to an internal 12-bit D/A converter latch, giving precise timing control over an analog output change.

The DAC667 is specified to  $\pm 1/2$ LSB maximum linearity error at  $+25^{\circ}$ C. The DAC667 is guaranteed monotonic over the specification temperature range. The DAC667 is available in 28-pin, 0.6" wide plastic DIP package.

© 1990 Burr-Brown Corporation

PDS-1091C

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

Printed in U.S.A. March, 1998

### **SPECIFICATIONS**

At  $T_A = +25$ °C,  $\pm 12$ V.  $\pm 15$ V power supplies, unless otherwise noted.

|                                                                                             | DAC667JP |                              |       |                         |  |

|---------------------------------------------------------------------------------------------|----------|------------------------------|-------|-------------------------|--|

| PARAMETER                                                                                   | MIN      | TYP                          | MAX   | UNITS                   |  |

| DIGITAL INPUTS                                                                              |          |                              |       |                         |  |

| Resolution                                                                                  |          |                              | 12    | Bits                    |  |

| Logic Levels (TTL Compatible, T <sub>MIN</sub> to T <sub>MAX</sub> ) <sup>(1)</sup>         |          |                              |       |                         |  |

| V <sub>IH</sub> (Logic 1)                                                                   | +2       |                              | +5.5  | l v                     |  |

| V <sub>II</sub> (Logic 0)                                                                   | 0        |                              | +0.8  | l v                     |  |

| $I_{IH}(VI_{H} = 5.5V)$                                                                     |          | 3                            | 10    | μΑ                      |  |

| $I_{\rm IL} \left( V_{\rm IL} = 0.8 V \right)$                                              |          | 1                            | 5     | μA                      |  |

| ACCURACY                                                                                    |          |                              |       |                         |  |

| Linearity Error at +25°C                                                                    |          | ±1/4                         | ±1/2  | LSB                     |  |

| $T_A = T_{MIN}$ to $T_{MAX}$                                                                |          | ±1/2                         | ±3/4  | LSB                     |  |

| Differential Linearity Error at +25°C                                                       |          | ±1/2                         | ±3/4  | LSB                     |  |

|                                                                                             | l        |                              |       | LSB                     |  |

| T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> Gain Error <sup>(2)</sup>             | lvi      | onotonicity Guarante    ±0.1 |       | % of FSR <sup>(3)</sup> |  |

|                                                                                             |          |                              | ±0.2  |                         |  |

| Unipolar Offset Error <sup>(2)</sup>                                                        |          | ±1                           | ±2    | LSB                     |  |

| Bipolar Zero <sup>(2)</sup>                                                                 |          | ±0.05                        | ±0.1  | % of FSR                |  |

| DRIFT                                                                                       |          | 1                            |       |                         |  |

| Differential Linearity                                                                      |          | ±2                           |       | ppm of FSR/°C           |  |

| Gain (Full Scale), $T_A = +25^{\circ}C$ to $T_{MIN}$ or $T_{MAX}$                           |          | ±5                           | ±30   | ppm of FSR/°C           |  |

| Unipolar Offset, $T_A = +25^{\circ}C$ to $T_{MIN}$ or $T_{MAX}$                             |          | ±1                           | ±3    | ppm of FSR/°C           |  |

| Bipolar Zero, $T_A = +25$ °C to $T_{MIN}$ or $T_{MAX}$                                      |          | ±5                           | ±10   | ppm of FSR/°C           |  |

| CONVERSION SPEED                                                                            |          |                              |       |                         |  |

| Settling Time to $\pm 0.01\%$ of FSR for FSR Change (2k $\Omega$    500pF Load, $C_F = 0$ ) |          |                              |       |                         |  |

| With 10kΩ Feedback                                                                          |          | 3                            | 4     | μs                      |  |

| With 5kΩ Feedback                                                                           |          | 2                            | 3     | μs                      |  |

| For LSB Change                                                                              |          | 2                            | _     | με                      |  |

| Slew Rate                                                                                   | 8        | _                            |       | V/μs                    |  |

| ANALOG OUTPUT                                                                               |          |                              |       |                         |  |

| Ranges <sup>(4)</sup>                                                                       |          | :2.5, ±5, ±10, +5, +         | n     | l v                     |  |

| Output Current                                                                              | ±5       | 1                            | I     | mA                      |  |

| Output Impedance (DC)                                                                       |          | 0.05                         |       | Ω                       |  |

| Short Circuit Current                                                                       |          | 0.00                         | 40    | mA                      |  |

| REFERENCE OUTPUT                                                                            | 9.9      | 10                           | 10.1  | T v                     |  |

| External Current                                                                            | 0.1      | 1                            | 10.1  | l mA                    |  |

|                                                                                             |          |                              |       | 1                       |  |

| POWER SUPPLY SENSITIVITY $V_{CC} = +11.4 \text{ to } +16.5 \text{VDC}$                      |          | 5                            | 10    | ppm of FS/%             |  |

|                                                                                             |          | 5                            | 10    | 1 '''                   |  |

| V <sub>EE</sub> = -11.4 to -16.5VDC                                                         |          | 5                            | 10    | ppm of FS/%             |  |

| POWER SUPPLY REQUIREMENTS                                                                   |          | 140 145                      |       |                         |  |

| Rated Voltages                                                                              |          | ±12, ±15                     |       | l v                     |  |

| Range <sup>(4)</sup>                                                                        | ±11.4    |                              | ±16.5 | V                       |  |

| Supply Current                                                                              |          |                              |       |                         |  |

| +11.4 to +16.5VDC                                                                           |          | 14                           | 17    | mA                      |  |

| -11.4 to -16.5VDC                                                                           |          | 9                            | 12    | mA                      |  |

| TEMPERATURE RANGE                                                                           |          |                              |       |                         |  |

| Specification                                                                               | 0        |                              | +70   | °C                      |  |

| Operating                                                                                   | -40      |                              | +85   | °C                      |  |

| Storage                                                                                     | -65      |                              | +125  | <b>I</b> ∘c             |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Power Ground                                        |

|------------------------------------------------------------------------|

| V <sub>FF</sub> to Power Ground                                        |

| Digital Inputs (Pins 11–15, 17–28) to Power Ground1V to +7V            |

| Ref In to Reference Ground                                             |

| Bipolar Offset to Reference Ground ±12V                                |

| 10V Span Resistor to Reference Ground ±12V                             |

|                                                                        |

| 20V Span Resistor to Reference Ground                                  |

| Ref Out, V <sub>OUT</sub> (Pins 6, 9)Indefinite Short to Power Ground, |

| Momentary Short To V <sub>cc</sub>                                     |

| Power Dissipation                                                      |

## **ELECTROSTATIC** DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE            | TEMPERATURE<br>RANGE | LINEARITY ERROR<br>max at 25°C | GAIN TC, max<br>(ppm/°C) | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|----------------------|--------------------------------|--------------------------|------------------------------------------|

| DAC667JP | 28-Pin Plastic DIP | 0°C to +70°C         | ±1/2LSB                        | ±30                      | 215                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

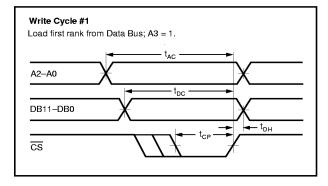

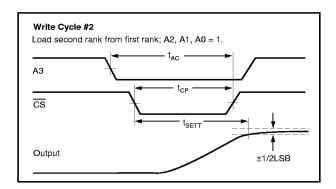

#### **TIMING SPECIFICATIONS**

| SYMBOL                                                                                     | PARAMETER                    | MIN | TYP | MAX | UNITS |  |

|--------------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|-------|--|

| t <sub>DC</sub>                                                                            | Data Valid to End of CS      | 50  | -   | -   | ns    |  |

| t <sub>AC</sub>                                                                            | Address Valid to End of CS   | 100 | _   | -   | ns    |  |

| t <sub>CP</sub>                                                                            | CS Pulse Width               | 100 | _   | _   | ns    |  |

| t <sub>DH</sub>                                                                            | Data Hold Time               | 0   | _   | _   | ns    |  |

| t <sub>SETT</sub>                                                                          | Output Voltage Settling Time | -   | 2   | 4   | μs    |  |

| All models, $T_A = +25^{\circ}C$ , $V_{CC} = +12V$ or $+15V$ , $V_{EE} = -12V$ or $-15V$ . |                              |     |     |     |       |  |

#### **TIMING DIAGRAMS**

## DISCUSSION OF SPECIFICATIONS

#### **LINEARITY ERROR**

Linearity error is defined as the deviation of the analog output from a straight line drawn between the end points (digital inputs all ones and all zeros). DAC667 linearity error is specified at  $\pm 1/4$ LSB max at  $\pm 1/2$ LSB max for J grade.

#### **DIFFERENTIAL LINEARITY ERROR**

Differential linearity error (DLE) is the deviation from a 1LSB output change from one adjacent state to the next. A DLE specification of 1/2LSB means that the output step size can range from 1/2LSB to 3/2LSB when the digital input code changes from one code word to the adjacent code word. If the DLE is more positive than –1LSB, the D/A is said to be monotonic.

#### MONOTONICITY

A D/A converter is monotonic if the output either increases or remains the same for increasing digital input values. The DAC667 is monotonic over the specification temperature range.

#### **DRIFT**

Gain drift is a measure of the change in the full scale range (FSR) output over the specification temperature range. Gain drift is expressed in parts per million per degree Celsius (ppm/°C).

Unipolar offset drift is measured with a data input of  $000_{\rm HEX}$ . The D/A is configured for unipolar output. Unipolar offset drift is expressed in parts per million of full scale range per degree Celsius (ppm of FSR/°C).

Bipolar zero drift is measured with a data input of  $800_{\rm HEX}$ . The D/A is configured for bipolar output. Bipolar zero drift is expressed in parts per million of full scale range per degree Celsius (ppm of FSR/°C).

#### **SETTLING TIME**

Settling time is the total time (including slew time) for the output to settle to within an error band around its final value after a change in input. Three settling times are specified to  $\pm 0.01\%$  of full scale range (FSR): two for FSR output changes of 20V (10k $\Omega$  feedback) and 10V (5k $\Omega$  feedback), and one for a 1LSB change. The 1LSB change is measured at the major carry (7FF $_{\rm HEX}$  to 800 $_{\rm HEX}$ , and 800 $_{\rm HEX}$  to 7FF $_{\rm HEX}$ ), the input transition at which worst-case settling time occurs.

#### **OPERATION**

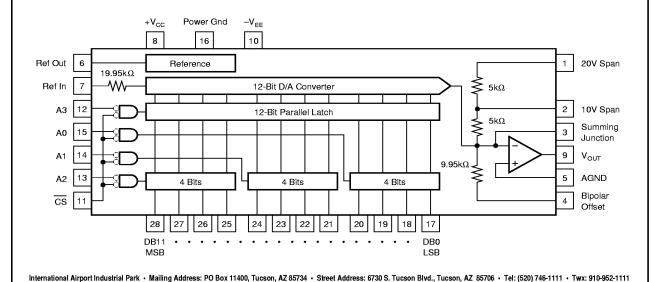

DAC667 is a monolithic integrated-circuit 12-bit D/A converter. It is complete with 12-bit D/A switches and ladder network, voltage reference, output amplifier and microprocessor bus interface as shown in the front-page diagram.

#### INTERFACE LOGIC

The bus interface logic of the DAC667 consists of four independently addressable latches in two ranks. The first rank consists of three four-bit input latches which can be loaded directly from a 4-, 8-, 12- or 16-bit microprocessor/microcontroller bus. These latches hold data temporarily while a complete 12-bit word is assembled before loading it into the second rank of latches. This double buffered organization prevents the generation of spurious analog output values while the complete word is being assembled.

All latches are level-triggered. Data present when the control signals are logic 0 will enter the latch. When the control signals return to logic 1, the data is latched. A truth table for the control signals is presented in Table I.

| cs    | А3              | <b>A</b> 2 | A1 | A0 | OPERATION                             |  |  |

|-------|-----------------|------------|----|----|---------------------------------------|--|--|

| 1     | Х               | Х          | Х  | Х  | No Operation                          |  |  |

| Х     | 1               | 1          | 1  | 1  | No Operation                          |  |  |

| 0     | 1               | 1          | 1  | 0  | Enable Four LSBs of First Rank        |  |  |

| 0     | 1               | 1          | 0  | 1  | Enable Four Middle Bits of First Rank |  |  |

| 0     | 1               | 0          | 1  | 1  | Enable Four MSBs of First Rank        |  |  |

| 0     | 0               | 1          | 1  | 1  | Loads Second Rank from First Rank     |  |  |

| 0     | 0               | 0          | 0  | 0  | All Latches Transparent               |  |  |

| X = D | X = Don't care. |            |    |    |                                       |  |  |

TABLE I. DAC667 Truth Table.

It is permissible to enable more than one of the latches simultaneously. If a first rank latch is enabled coincident with the second rank latch, the data will reach the second rank correctly if the timing specifications on page 2 are met.

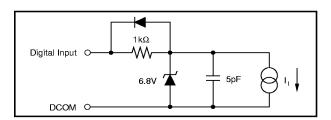

#### LOGIC INPUT COMPATIBILITY

The DAC667 digital inputs are TTL compatible (1.4V switching level) with a low leakage, high input impedance. Thus the inputs are suitable for being driven by any type of 5V logic. An equivalent circuit of a digital input is shown in Figure 1.

FIGURE 1. Equivalent Digital Input Circuit.

DAC667 data inputs will float to logic 1 and control inputs will float to logic 0 if left open. It is recommended that any unused inputs be connected to power common to improve noise immunity.

#### **INPUT CODING**

The DAC667 accepts positive-true binary input codes.

Input coding for unipolar analog output is straight binary (USB), where all zeros  $(000_{HEX})$  on the data inputs gives a

zero analog output and all ones (FFF<sub>HEX</sub>) gives an analog output 1LSB below full scale.

Input coding for bipolar analog outputs is bipolar offset binary (BOB), where an input code of  $000_{\rm HEX}$  gives a minus full-scale output, an input of FFF $_{\rm HEX}$  gives an output 1LSB below positive full scale, and zero occurs for an input code of  $800_{\rm HEX}$ .

The DAC667 can be used with two's complement coding if a logic inverter is used ahead of the MSB input (DB11).

#### INTERNAL/EXTERNAL REFERENCE USE

DAC667 contains a +10V reference which is trimmed to typically  $\pm 0.2\%$  and tested and guaranteed to  $\pm 1\%.$   $V_{REFOUT}$  must be connected to  $V_{REF\,IN}$  through a gain adjust resistor with a nominal value of  $50\Omega.$  A trim potentiometer with a nominal value of  $100\Omega$  can be used to provide adjustment to zero gain error. If an external 10.000V reference is used, it may be necessary to increase the trim range slightly.

The reference output may be used to drive external loads, sourcing up to 5mA. The load current should be constant, otherwise the gain (and bipolar offset, if connected) of the converter will vary.

It is possible to use references other than +10V. The recommended range of reference voltage is from +8V to +11V, which allows both 8.192V and 10.24V ranges to be used. The DAC667 is optimized for fixed-reference applications. If the reference voltage is expected to vary over a wide range, a CMOS multiplying D/A is a better choice.

#### **GAIN AND OFFSET ADJUSTMENTS**

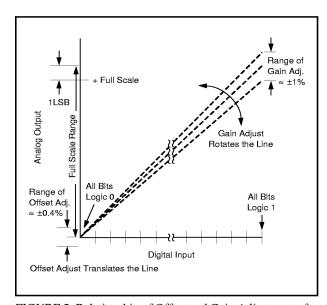

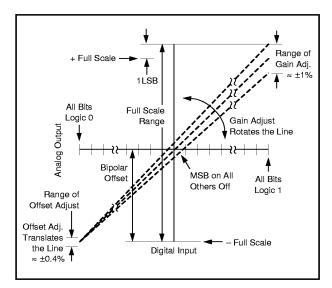

Figures 2 and 3 illustrate the relationship of offset and gain adjustments to a unipolar- and a bipolar-connected DAC667. Offset should be adjusted first to avoid interaction of adjustments.

FIGURE 2. Relationship of Offset and Gain Adjustments for a Unipolar D/A Converter.

FIGURE 3. Relationship of Offset and Gain Adjustments for a Bipolar D/A Converter.

#### Offset Adjustment

For unipolar (USB) operation, apply the digital input code that should produce zero voltage output and adjust the offset potentiometer for zero output. For bipolar (BOB, BTC) operation, apply the digital input code that produces the maximum negative output voltage and adjust the offset potentiometer for minus full scale voltage. See Table II for calibration values and codes.

| DIGITAL            | ANALOG OUTPUT |                |          |                |           |  |  |

|--------------------|---------------|----------------|----------|----------------|-----------|--|--|

| INPUT              | 0 to +5V      | 0 to +10V      | ±2.5V    | ±5V            | ±10V      |  |  |

| FFF <sub>HEX</sub> | +4.9987V      | +9.9976V       | +2.4987V | +4.9976V       | +9.9951V  |  |  |

| 800 <sub>HEX</sub> | +2.5000V      | +5.0000V       | 0.0000∨  | 0.0000V        | 0.0000V   |  |  |

| 7FF <sub>HEX</sub> | +2.4987V      | +4.9976V       | -0.0013V | -0.0024V       | -0.0049V  |  |  |

| 000 <sub>HEX</sub> | 0.0000V       | 0.0000V        | -2.5000V | -5.0000V       | -10.0000V |  |  |

| 1LSB               | 1.22mV        | 2.44m <b>V</b> | 1.22mV   | 2.44m <b>V</b> | 4.88mV    |  |  |

TABLE II. Calibration Values.

#### **Gain Adjustment**

For either unipolar or bipolar operation, apply the digital input that gives the maximum positive voltage output. Adjust the gain potentiometer for this positive full scale voltage. See Table II for calibration values.

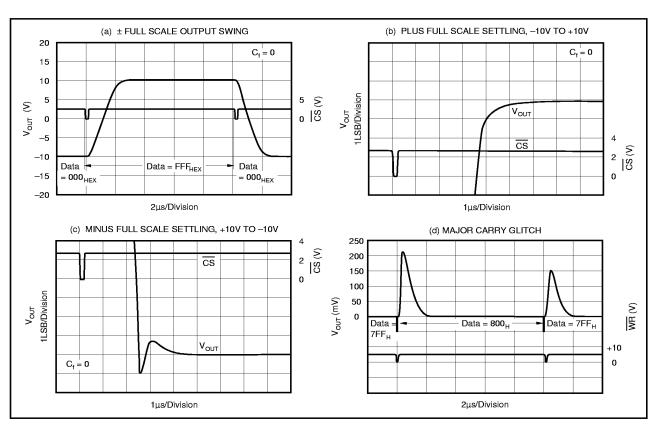

## SETTLING TIME PERFORMANCE

The switches, reference and output amplifier of the DAC667 are designed for optimum settling time performance (Figure 4). Figure 4a shows the full scale range step response,  $V_{OUT}-10V$  to +10V to -10V, for data input  $000_{HEX}$  to  $FFF_{HEX}$  to  $000_{HEX}$ . Figure 4b shows the settling time response at plus full scale (+10V) for an output transition from -10V to +10V. Figure 4c shows the settling time response at minus

**DAC667**

full scale (-10V) for an output transition from +10V to -10V. Figure 4d shows the major carry glitch response for input code transitions  $7FF_{\rm HEX}$  to  $800_{\rm HEX}$  and for  $800_{\rm HEX}$  to  $7FF_{\rm HEX}$ .

Unlike the Analog Devices AD667, the Burr-Brown DAC667 does not require an external capacitor ( $C_f = 20 \mathrm{pF}$ ) across  $R_{SPAN}$  to eliminate overshoot. Using the 20pF with the Burr-Brown DAC667 increases the settling time about one microsecond. The DAC667 settling time is specified at 7 $\mu$ s maximum. The AD667 is specified at 4 $\mu$ s maximum.

#### INSTALLATION

#### **POWER SUPPLY CONNECTIONS**

Note that the metal lid of the ceramic-packaged DAC667 is connected to  $-V_{\rm EE}$ . Take care to avoid accidental short circuits in tightly spaced installations.

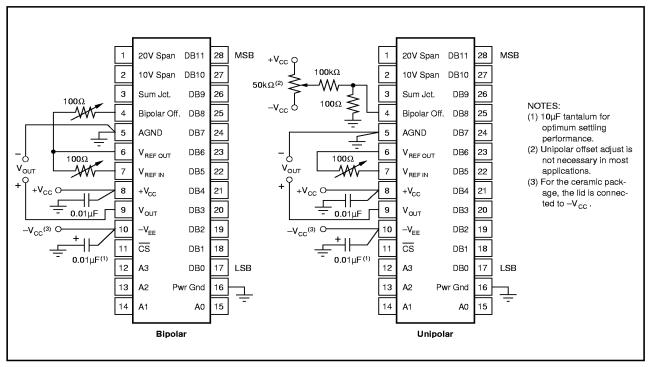

Power supply decoupling capacitors should be added as shown in Figure 5. Best settling performance occurs using a  $1\mu F$  to  $10\mu F$  tantalum capacitor at  $-V_{EE}$ . Applications with less critical settling time may be able to use  $0.01\mu F$  at  $-V_{EE}$  as well as at  $+V_{CC}$ . The capacitors should be located close to the DAC667 package.

DAC667 features separate digital and analog power supply returns to permit optimum connections for low noise and high speed performance. It is recommended that both power ground (pin 16) and analog ground (AGND, pin 5) be connected directly to a ground plane under the package. If a ground plane is not used, connect the AGND and power ground pins together close to the package. Since the reference point for  $V_{\rm OUT}$  and  $V_{\rm REF\,OUT}$  is the AGND pin, it is also important to connect the load directly to the AGND pin.

The change in current in the AGND pin due to an input data word change from  $000_{HEX}$  to FFF<sub>HEX</sub> is only 1mA.

## OUTPUT VOLTAGE SWING AND RANGE CONNECTIONS

The DAC667 output amplifier can provide  $\pm 10V$  output swing while operating on  $\pm 11.4V$  supplies. The Analog Devices AD667 requires a minimum of  $\pm 12.5V$  to achieve an output swing of  $\pm 10V$ .

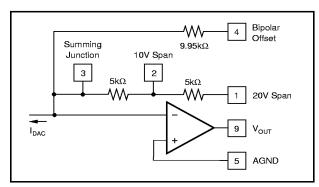

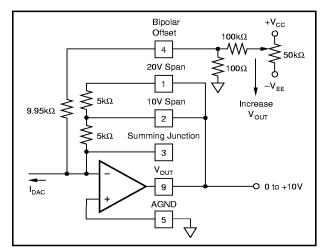

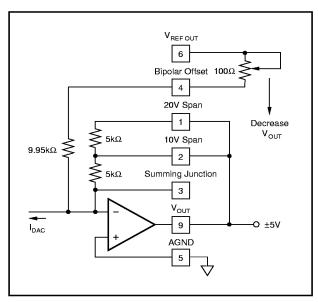

Internal scaling resistors provided in the DAC667 may be connected to produce bipolar output voltage ranges of  $\pm 10$ V,  $\pm 5$ V or  $\pm 2.5$ V or unipolar output voltage ranges of 0 to  $\pm 5$ V or 0 to  $\pm 10$ V. Refer to Figures 6, 7 and 8. Connections for various output ranges are shown in Table III.

The internal feedback resistors ( $5k\Omega$ ) and the bipolar offset resistor ( $9.95k\Omega$ ) are trimmed to an absolute tolerance of about  $\pm 10\%$ .

FIGURE 4. Settling Time Performance,  $Z_{LOAD} = 2k\Omega \parallel 500 pF$ .

FIGURE 5. Power Supply, Gain and Offset Connections.

FIGURE 6. Output Amplifier Voltage Range Scaling Circuit.

FIGURE 7. 0 to +10V Unipolar Voltage Output.

FIGURE 8. ±5V Bipolar Voltage Output.

### MICROCOMPUTER BUS INTERFACING

#### **8-BIT BUS INTERFACE**

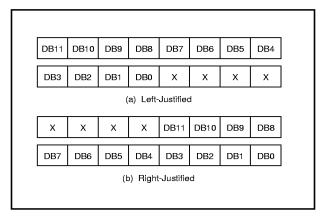

The DAC667 interfaces easily to 8-bit microprocessor systems of all types. The control logic makes possible the use of right- or left-justified data formats. Data formats for 8-bit buses are illustrated in Figure 9.

**DAC667**

| OUTPUT    | DIGITAL         | CONNECT  | CONNECT  | CONNECT  | CONNECT PIN 4 TO                                                                                                                                                                                               |

|-----------|-----------------|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RANGE     | INPUT CODES     | PIN 9 TO | PIN 1 TO | PIN 2 TO |                                                                                                                                                                                                                |

| ±10V      | Offset Binary   | 1        | 9        | NC       | 6 (Through 50Ω fixed or 100Ω trim resistor.) 6 (Through 50Ω fixed or 100Ω trim resistor.) 6 (Through 50Ω fixed or 100Ω trim resistor.) 5 (Or optional trim. See Figure 7.) 5 (Or optional trim. See Figure 7.) |

| ±5V       | Offset Binary   | 1 and 2  | 2 and 9  | 1 and 9  |                                                                                                                                                                                                                |

| ±2.5V     | Offset Binary   | 2        | 3        | 9        |                                                                                                                                                                                                                |

| 0 to +10V | Straight Binary | 1 and 2  | 2 and 9  | 1 and 9  |                                                                                                                                                                                                                |

| 0 to +5V  | Straight Binary | 2        | 3        | 9        |                                                                                                                                                                                                                |

TABLE III. Output Voltage Range Connections.

FIGURE 9. 12-Bit Data Formats for 8-Bit Systems.

Whenever a 12-bit D/A is loaded from an 8-bit bus, two bytes are required. If the software program considers the data to be a 12-bit binary fraction (between 0 and 4095/4096), the data is left-justified, with the eight most significant bits in one byte and the remaining bits in the upper half of another byte. Right-justified data calls for the eight least significant bits to occupy one byte, with the four most significant bits residing in the lower half of another byte, simplifying integer arithmetic.

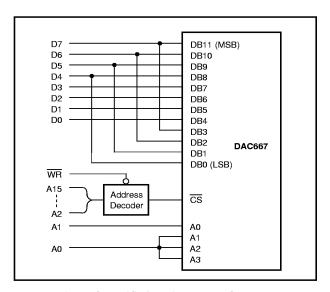

Figure 10 shows an addressing scheme for use with a DAC-667 set up for left-justified data in an 8-bit system. The base address is decoded from the high-order address bits and the resultant active-low signal is applied to  $\overline{\text{CS}}$ . The two LSBs of the address bus are connected as shown to the DAC667 address inputs. The latches now reside in two consecutive locations, with location X01 loading the four LSBs and location X10 loading the eight MSBs and updating the output.

FIGURE 10. Left-Justified 8-Bit Bus Interface.

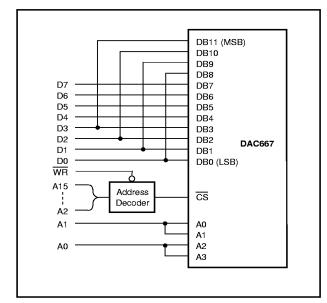

Right-justified data can also be accommodated as shown in Figure 11. The DAC667 still occupies two adjacent locations in the processor's memory map. Location X01 loads the eight LSBs and location X10 loads the four MSBs and updates the output.

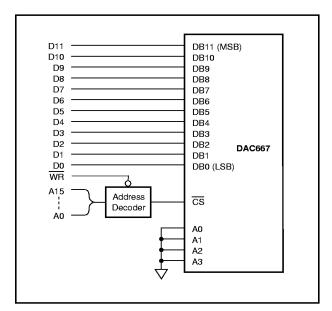

#### 12- AND 16-BIT BUS INTERFACES

For operation with 12- and 16-bit buses, all four address lines (A0 through A3) are connected to logic 0, and the latch is enabled by  $\overline{CS}$  asserted low. The DAC667 thus occupies a single memory location.

This configuration uses the first and second rank registers simultaneously. The  $\overline{CS}$  input can be driven from an active-low decoded address. It should be noted that any data bus activity during the period when  $\overline{CS}$  is low will cause activity at the DAC667 output. If data is not guaranteed stable during this period, the second rank register can be used to provide double buffering. See Figure 12.

FIGURE 12. Connections for 12- and 16-Bit Bus Interface.

FIGURE 11. Right-Justified 8-Bit Bus Interface.